# Data Flow in the Mu3e Data Acquisition System

### DISSERTATION

zur Erlangung des Grades "Doktor der Naturwissenschaften" am Fachbereich Physik, Mathematik und Informatik der Johannes Gutenberg-Universität in Mainz

vorgelegt von

Marius Köppel

geboren in Bühl

Mainz, den 10.01.2024

#### **Abstract**

The discovery of the Higgs boson by the ATLAS [1] and Compact Muon Solenoid Experiment (CMS) [2] experiments at CERN's Large Hadron Collider (LHC) [3] in 2012 marked a milestone in particle physics, completing the Standard Model of particle physics (SM) as a self-consistent theory. However, the observation of neutrino oscillations shows violations of lepton-flavour conservation, hinting at physics beyond the SM. Charged lepton-flavour violation (CLFV) decays, such as  $\mu^+ \to e^+e^-e^+$ , remain undetected and would be a definitive sign of new physics.

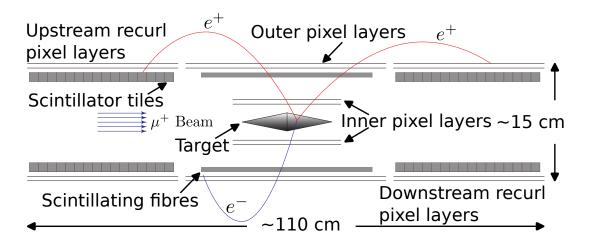

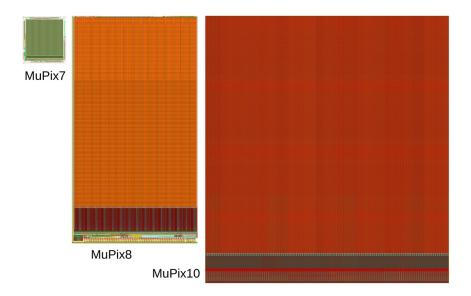

The Mu3e experiment, currently under construction at the Paul Scherrer Institute (PSI), is specifically designed to observe the decay  $\mu^+ \to e^+e^-e^+$ , a process exceptionally rare in the extension of the SM with neutrino oscillation, but enhanced in many theories beyond the SM. Achieving high sensitivity is crucial to detect such a rare decay. Mu3e aims for an ultimate sensitivity of one in  $10^{16}$  muon decays. In its initial phase, Mu3e aims to achieve a branching ratio sensitivity of  $2 \cdot 10^{-15}$ , analysing  $1 \times 10^8$  muon decays per second over a year of data collection. The experiment uses highly granular detectors consisting of thin High-Voltage Monolithic Active Pixel Sensors (HV-MAPS), the MuPix chip, and scintillating timing detectors, generating approximately  $100 \, \text{Gbit/s}$  of data at these particle rates.

The Mu3e data acquisition (DAQ) system, based on field programmable gate arrays (FPGAs), is a crucial component of the experiment. It employs a trigger-less readout system to deal with the randomly distributed decay particles of muons at rest. The system sorts, time-aligns, and analyses data in real time, using a filter farm of graphics processing units (GPUs) for track reconstruction.

This thesis presents the integration of subdetectors into the Mu3e DAQ system, focusing on the scintillating timing detectors, time-alignment, and data flow within the filter farm. It discusses the requirements for building the Mu3e DAQ system, including data protocols, data flow algorithms, and online data quality checks. Integration runs and testbeams at various facilities, including Deutsches Elektronen-Synchrotron (DESY), Mainz Microtron (MAMI), and PSI, have been instrumental in the refining of the system.

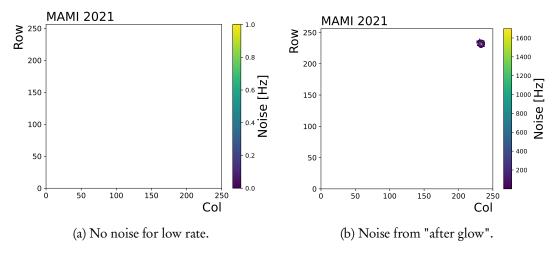

Moreover, this work encompasses irradiation studies of the MuPix10 chip at MAMI to understand its high-rate operation. In addition to research related to the Mu3e experiment, the development of a prototype detector for muon spin rotation ( $\mu$ SR) techniques using MuPix11 chips is presented. Initial tests in 2021 and a special run at PSI in 2023 demonstrated the first  $\mu$ SR signal detection using Si-Pixel detectors, marking the start of a novel methodology in this field.

#### Zusammenfassung

Die Entdeckung des Higgs-Bosons durch die Experimente ATLAS [1] und CMS [2] am LHC des CERNs im Jahr 2012 war ein Meilenstein in der Teilchenphysik und vervollständigte das Standardmodell der Teilchenphysik zu einer selbstkonsistenten Theorie. Die Beobachtung von Neutrino-Oszillationen zeigt jedoch Verstöße gegen die Lepton-Flavour-Erhaltung, was auf eine Physik jenseits des Standardmodells hindeutet. Geladene Lepton-Flavour-verletzende Zerfälle, wie  $\mu^+ \to e^+e^-e^+$ , wurden bisher nicht beobachtet und wären ein eindeutiges Zeichen für neue Physik.

Das Mu3e-Experiment, das derzeit am PSI aufgebaut wird, ist speziell darauf ausgelegt, den Zerfall  $\mu^+ \to e^+e^-e^+$  zu beobachten, einen Prozess, der in der Erweiterung des Standardmodells mit Neutrino-Oszillation außergewöhnlich selten ist, aber in vielen Theorien jenseits des SM verstärkt auftritt. Um einen solch seltenen Zerfall nachzuweisen, ist eine hohe Sensitivität entscheidend. Mu3e strebt eine ultimative Sensitivität von einem in  $10^{16}$  Myonenzerfällen an. In der Anfangsphase will Mu3e eine Sensitivität für das Verzweigungsverhältnis von  $2\cdot 10^{-15}$  erreichen, indem es  $1\times 10^8$  Myonenzerfälle pro Sekunde über ein Jahr der Datenerfassung analysiert. Das Experiment verwendet hochgranulare Detektoren, die auf dünnen HV-MAPS, dem MuPix-Chip und szintillierenden Zeitdetektoren basieren, und erzeugt bei diesen Teilchenraten etwa 100 Gbit/s an Daten.

Das Mu3e DAQ System, welche auf FPGAs aufbaut, ist ein entscheidendes Bauteil des Experiments. Sie verwendet ein triggerloses Auslesesystem, um mit den zufällig verteilten Zerfallsteilchen von ruhenden Myonen umzugehen. Das System sortiert und analysiert die Daten in Echtzeit und nutzt eine Filterfarm aus GPUs für die Spurrekonstruktion.

In dieser Arbeit wird die Integration von Subdetektoren in das Mu3e DAQ – System vorgestellt, wobei der Schwerpunkt auf den szintillierenden Zeitdetektoren, der Zeitausrichtung und dem Datenfluss innerhalb der Filterfarm liegt. Es werden die Anforderungen für den Aufbau des Mu3e DAQ – Systems erörtert, einschließlich Datenprotokollen, Datenflussalgorithmen und Online-Datenqualitätsprüfungen. Integrationsläufe und Teststrahlen an verschiedenen Einrichtungen, darunter DESY, MAMI und PSI, haben maßgeblich zur Evaluierung des Systems beigetragen.

Darüber hinaus umfasst diese Arbeit auch Bestrahlungsstudien des MuPix10-Chips am MAMI Beschleuniger, um dessen Betrieb bei hochen Teilchenraten zu verstehen. Zusätzlich zu den Forschungsarbeiten im Zusammenhang mit dem Mu3e-Experiment wird die Entwicklung eines Prototyps eines Detektors für  $\mu$ SR-Techniken unter Verwendung von MuPix11-Chips vorgestellt. Erste Tests im Jahr 2021 und ein spezieller Lauf am PSI im Jahr 2023 zeigen die erste  $\mu$ SR-Signaldetektion mit Si-Pixel-Detektoren und markierten den Beginn einer neuen Methodik in diesem Bereich.

## Contents

| I Introduction |      |                                                          |          |  |  |

|----------------|------|----------------------------------------------------------|----------|--|--|

| 1              | The  | orv                                                      | 3        |  |  |

| -              | 1.1  | The Standard Model of particle physics                   | 3        |  |  |

|                | 1.2  | Muon decays                                              | 7        |  |  |

|                | 1.2  | 1.2.1 Muon decays in the Standard Model                  | 7        |  |  |

|                |      | 1.2.2 Muon decays beyond the Standard Model              | 8        |  |  |

|                | 1.3  | Charged lepton-flavour violation experiments             | 9        |  |  |

|                | 1.5  | 1.3.1 SINDRUM                                            | 9        |  |  |

|                |      | 1.3.2 MEG and MEG II                                     | 10       |  |  |

|                |      | 1.3.2 WILO and WILO II                                   | 10       |  |  |

| 2              | Prin | ciples of Particle Detectors                             | 13       |  |  |

|                | 2.1  | Silicon detectors                                        | 13       |  |  |

|                | 2.2  | Principle of tracking detectors                          | 14       |  |  |

|                | 2.3  | Multiple Scattering                                      | 15       |  |  |

|                | 2.4  | High Voltage Monolithic Active Pixel Sensors             | 16       |  |  |

|                | 2.5  | Scintillating detectors                                  | 17       |  |  |

| 3              | Read | dout Electronics                                         | 19       |  |  |

|                | 3.1  | Field Programmable Gate Arrays (FPGAs)                   | 19       |  |  |

|                | 3.2  | Data Transmission in FPGAs                               | 21       |  |  |

|                | 3.3  | Basics of data transmission                              | 21       |  |  |

|                | 3.4  | Electrical data transmission and Telegrapher's Equations | 23       |  |  |

|                | 3.5  | Serial data links for Inter-device Communication         | 24       |  |  |

|                | 3.6  | High speed links in FPGAs                                | 27       |  |  |

|                | 3.7  | Optical data transmission                                | 31       |  |  |

|                | 3.8  | Bit Error Rate Tests                                     | 32       |  |  |

|                | 3.9  | Data readout via PCIe                                    | 32       |  |  |

| 4              | The  | The Mu3e Experiment 37                                   |          |  |  |

| 4              | 4.1  |                                                          | 38       |  |  |

|                | 4.2  | Signal and background processes                          | 39       |  |  |

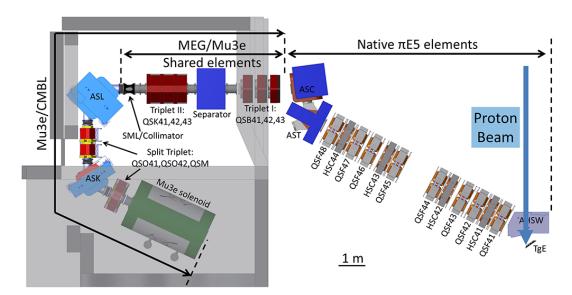

|                | 4.2  | Detector design                                          | 39<br>40 |  |  |

|                |      | 4.2.1 The Compact Muon Beam Line                         |          |  |  |

|                |      | 4.2.2 The Mu3e Target                                    | 43       |  |  |

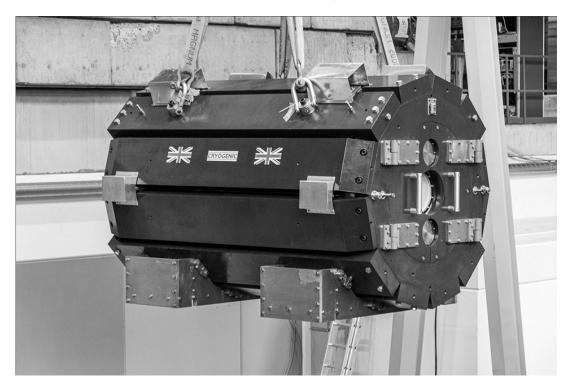

|                | 1.2  | 4.2.3 The Mu3e Magnet                                    | 43<br>44 |  |  |

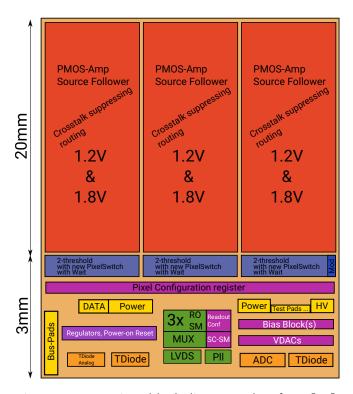

|                | 4.3  | MuPix Pixel Sensor                                       |          |  |  |

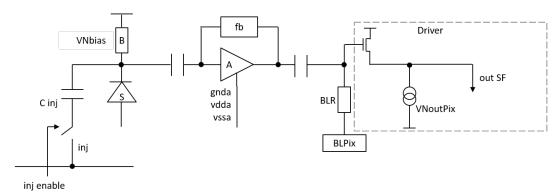

|                |      | 4.3.1 Pixel cell electronics                             | 46       |  |  |

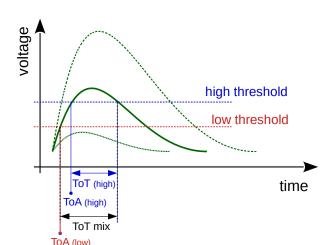

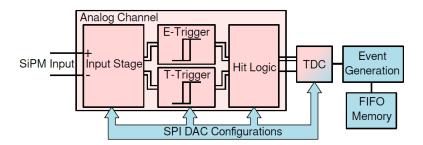

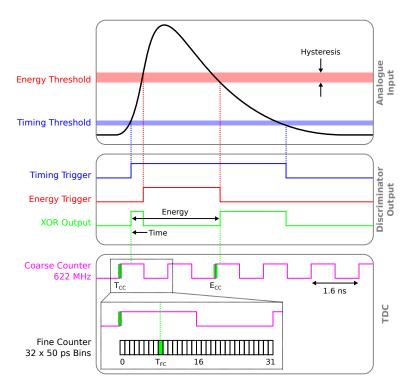

|                | 4.4  | The MuTRiG ASIC                                          | 48       |  |  |

|    | 4.5<br>4.6  | The scintillating fibre detector                    | 50<br>52     |  |

|----|-------------|-----------------------------------------------------|--------------|--|

| II | Tł          | ne Data Acquisition of the Mu3e Experiment          | 55           |  |

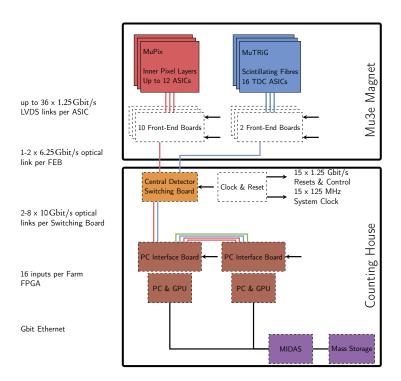

| 5  | <b>Mu</b> 3 | Be Data Acquisition System Overview of the Mu3e DAQ | <b>57</b> 57 |  |

|    | 5.2         | Clock and Reset System                              | 59           |  |

|    | 5.3         | Readout ASICs                                       | 59           |  |

|    | 5.4         | Data rate requirements                              | 60           |  |

|    | 5.5         | Related work of DAQ systems                         | 61           |  |

| 6  | Fron        | Front-end Board                                     |              |  |

|    | 6.1         | Front-end board                                     | 64           |  |

|    | 6.2         | Hit-time sorter                                     | 64           |  |

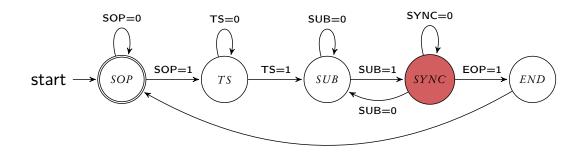

|    | 6.3         | Front-end board communication protocols             | 65           |  |

|    | 6.4         | Communication front-end boards to switching boards  | 65<br>66     |  |

|    |             | 6.4.1 MuPix communication protocol                  | 67           |  |

|    |             | 6.4.3 Slow control communication protocol           | 67           |  |

|    |             | 6.4.4 Run control signals                           | 68           |  |

|    |             | 6.4.5 Idle state                                    | 69           |  |

|    | 6.5         | Communication of clock and reset system             | 69           |  |

|    | 6.6         | The MuTRiG datapath                                 | 70           |  |

| 7  | Swit        | ching Board 73                                      |              |  |

|    | 7.1         | Overview of the Switching Board                     | 73           |  |

|    | 7.2         | Data flow of the Switching Board                    | 74           |  |

|    | 7.3         | Hit-time-alignment tree                             | 75           |  |

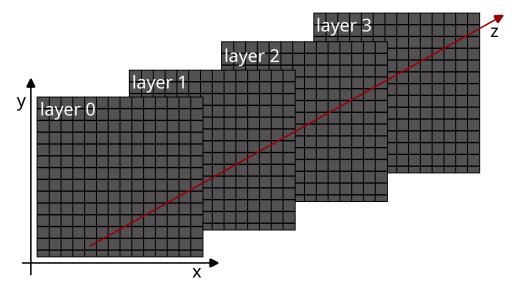

|    | 7.4         | Detector configuration                              | 77           |  |

| 8  |             | eiving board and Filter Farm                        | 79           |  |

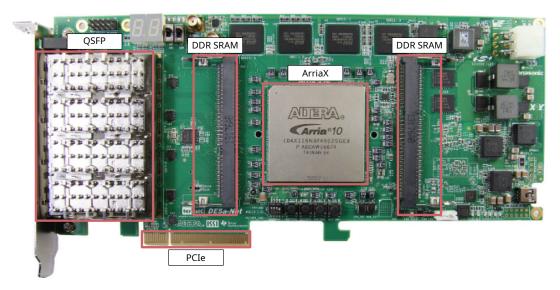

|    |             | Receiving board                                     | 79           |  |

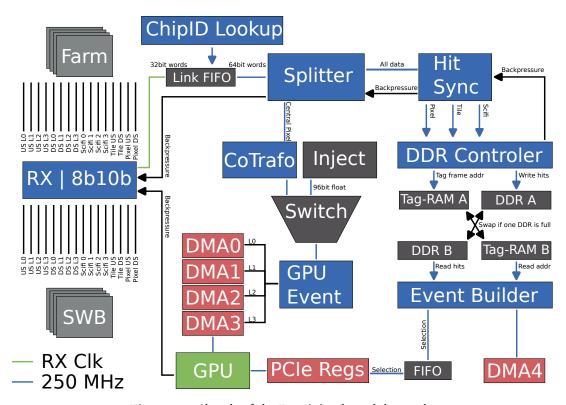

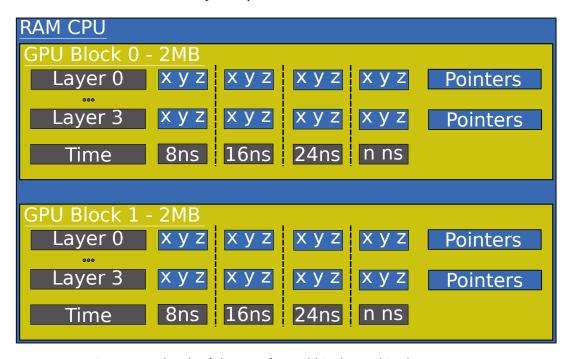

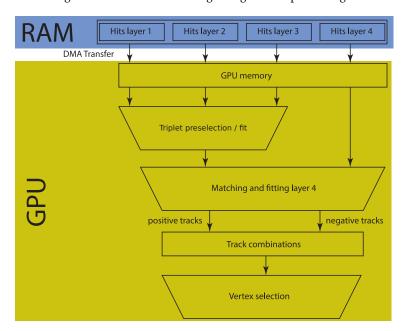

|    |             | Data flow of the Filter Farm                        | 80           |  |

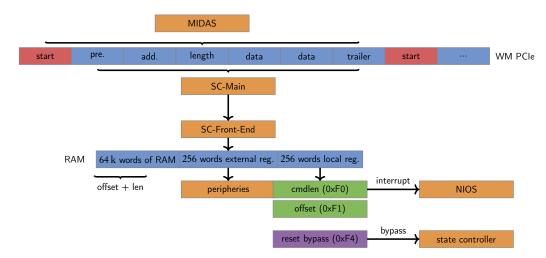

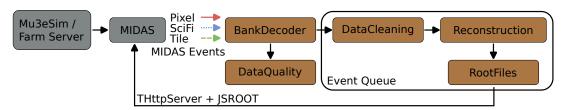

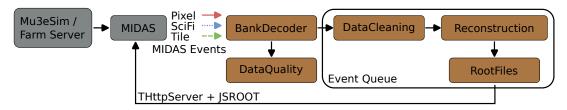

|    | 8.3<br>8.4  | MIDAS event builder                                 | 82<br>84     |  |

|    | 8.5         | Mu3e Online Analyzer                                | 85           |  |

|    | 8.6         | Online event selection                              | 86           |  |

|    | 0.0         |                                                     |              |  |

| II | I D         | Detector Integration                                | 89           |  |

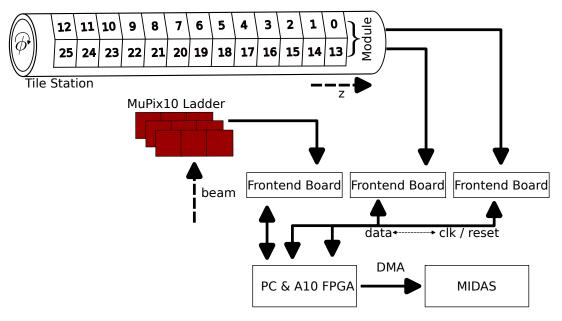

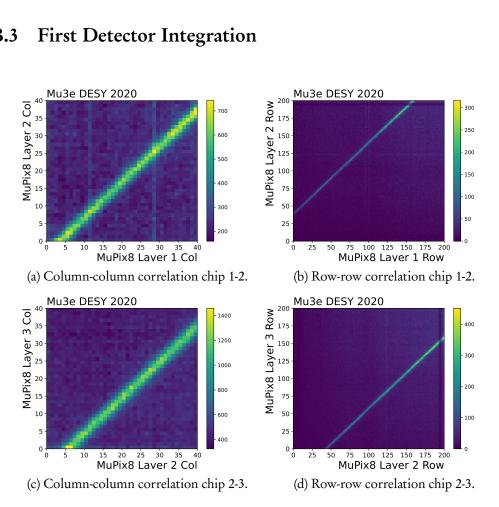

| 9  |             | t Detector Integration                              | 91           |  |

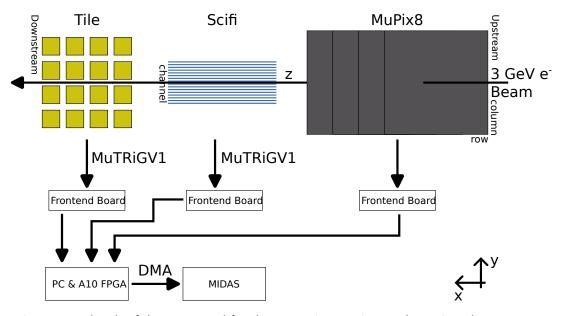

|    | 9.1         | DESY testbeam facility                              | 91           |  |

|    | 9.2         | DESY 2020 experimental setup                        | 91           |  |

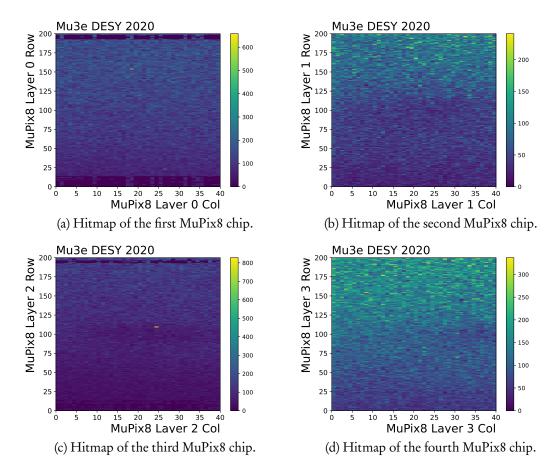

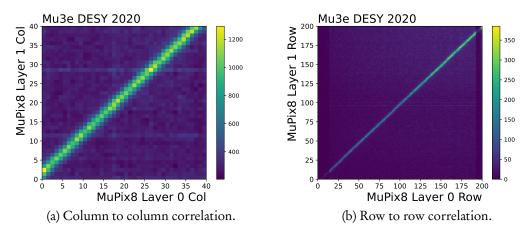

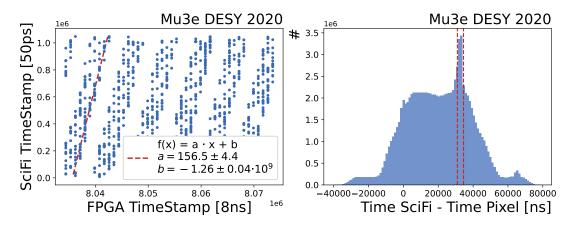

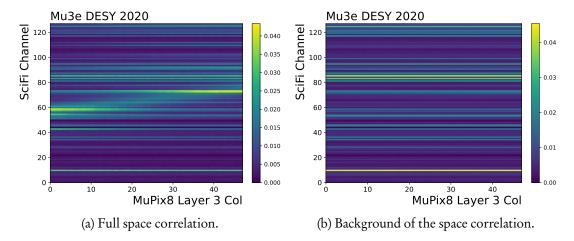

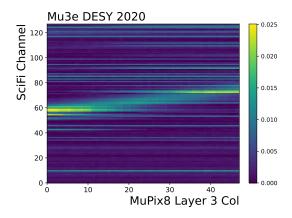

|    | 9.3         | DESY 2020 testbeam results                          | 92           |  |

### CONTENTS

| 10 | Front-end Board Synchronisation                   | 97  |

|----|---------------------------------------------------|-----|

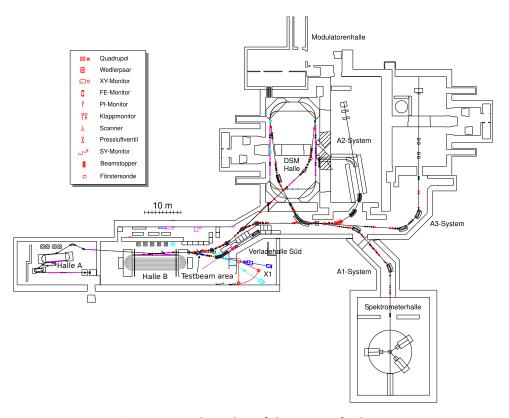

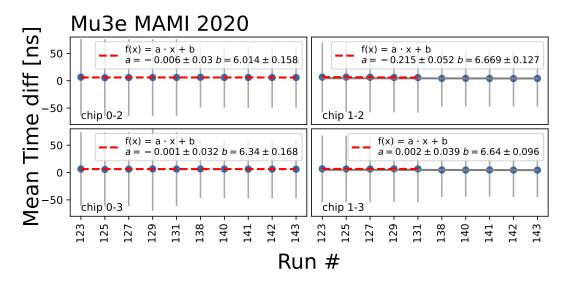

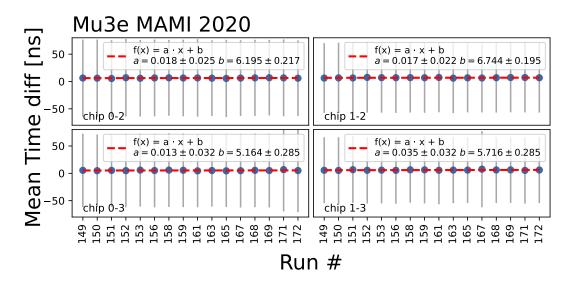

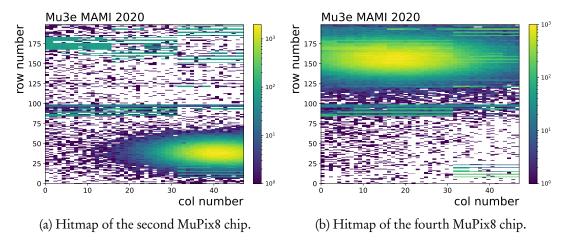

|    | 10.1 MAMI testbeam facility                       | 98  |

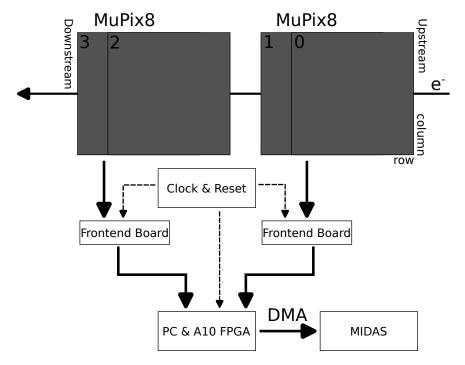

|    | 10.2 MAMI 2020 experimental setup                 | 98  |

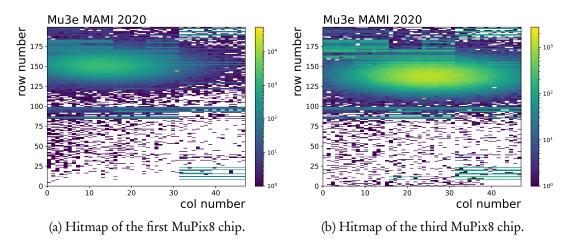

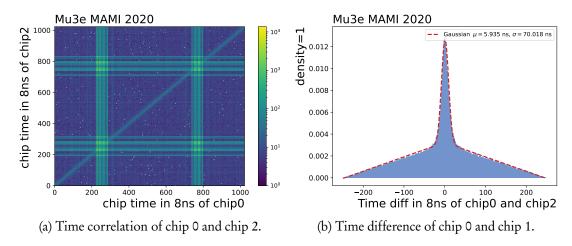

|    | 10.3 MAMI 2020 testbeam results                   | 99  |

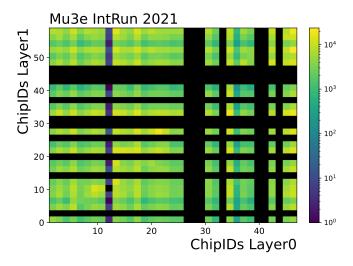

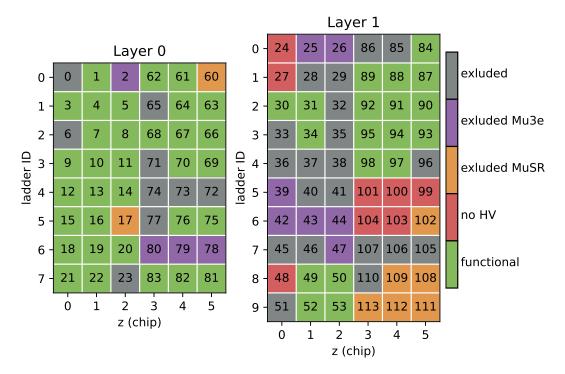

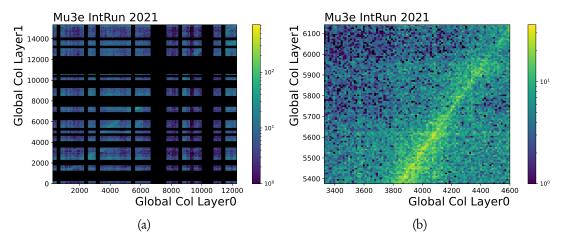

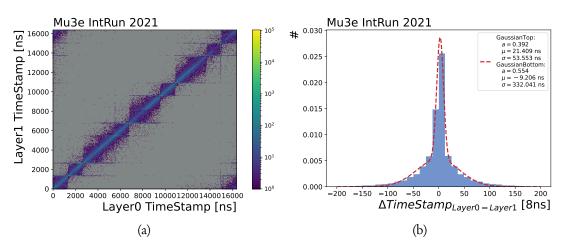

| 11 | Mu3e Integration Run 2021                         | 103 |

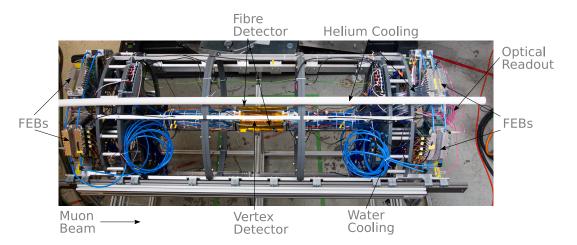

|    | 11.1 Mu3e Integration Run setup                   | 103 |

|    | 11.2 Mu3e Integration Run DAQ system              | 104 |

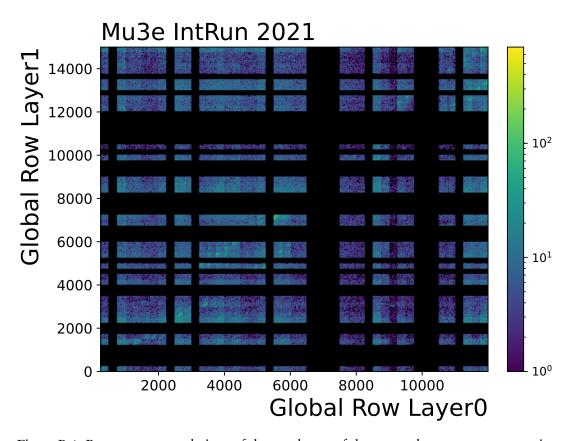

|    | 11.3 Results of the Mu3e Integration Run 2021     | 106 |

|    | 11.4 Results of the $\mu$ SR measurement          | 108 |

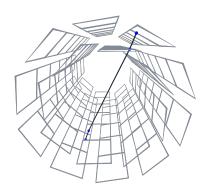

| 12 | Mu3e Cosmic Run 2022                              | 111 |

|    | 12.1 Mu3e Cosmic Run setup                        | 111 |

|    | 12.2 Mu3e Cosmic Run DAQ system                   | 113 |

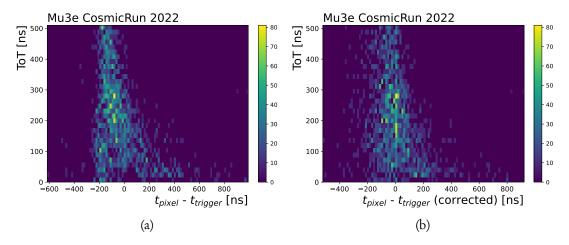

|    | 12.3 Data flow during the Mu3e Cosmic Run         | 113 |

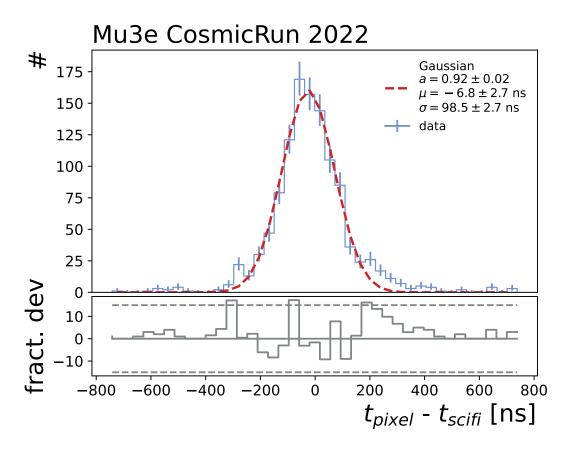

|    | 12.4 Timing studies during the Mu3e Cosmic Run    | 114 |

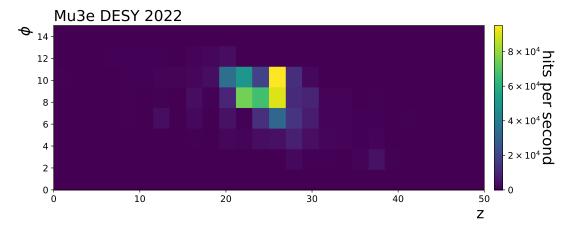

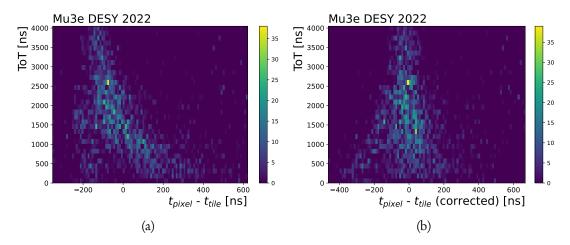

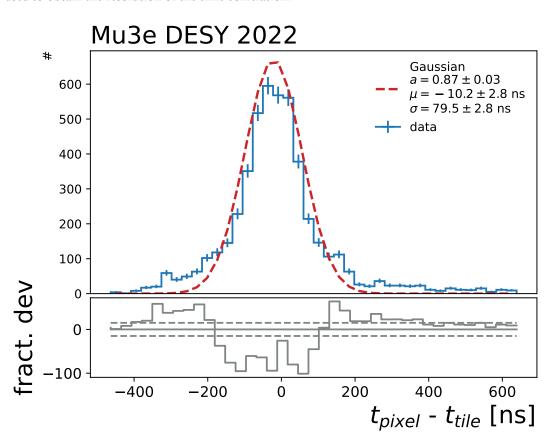

| 13 | Tile Integration                                  | 117 |

| 13 | 13.1 Tile Integration Run setup                   | 118 |

|    | 13.2 Rate monitoring tests                        | 118 |

|    | 13.3 Time correlation studies                     | 119 |

|    |                                                   |     |

| IV | Irradiation and $\mu$ SR Studies                  | 121 |

| 14 | MuPix Irradiation Studies                         | 123 |

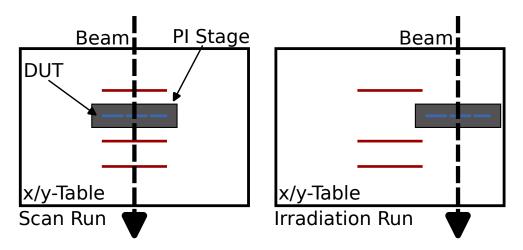

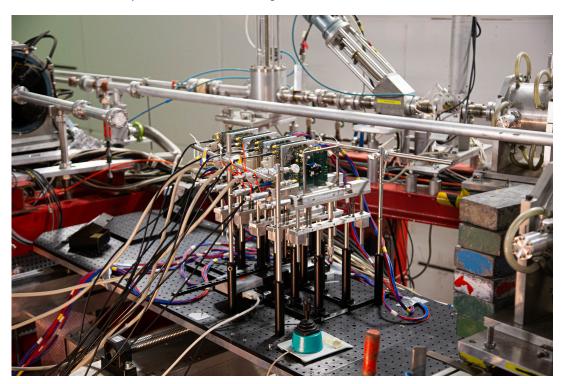

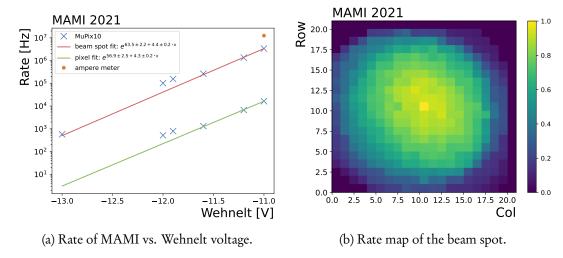

|    | 14.1 Experimental setup                           | 124 |

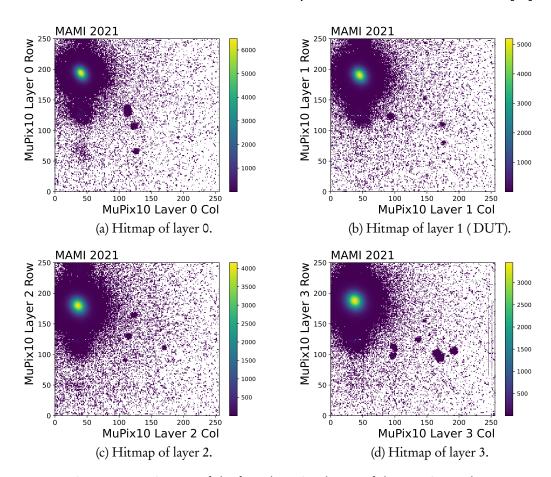

|    | 14.2 Analysis flow                                | 126 |

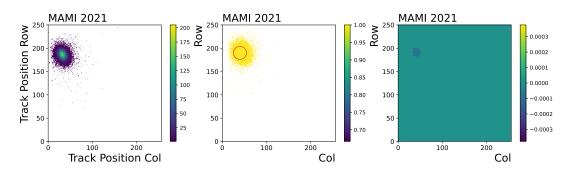

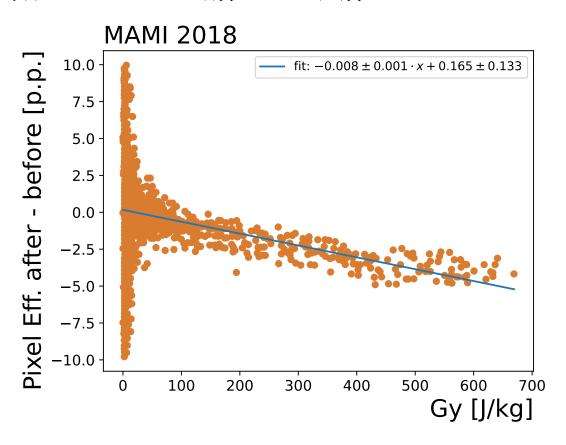

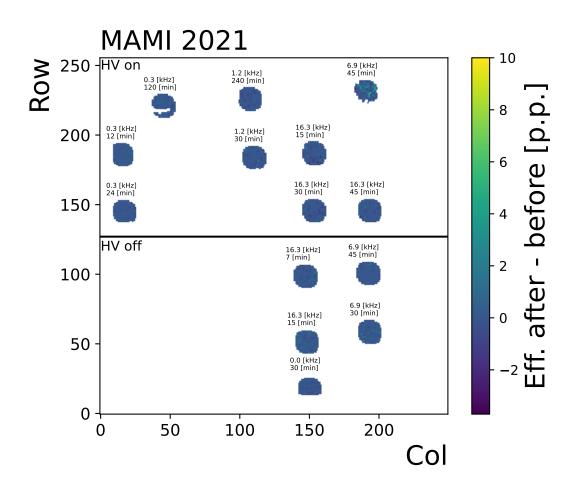

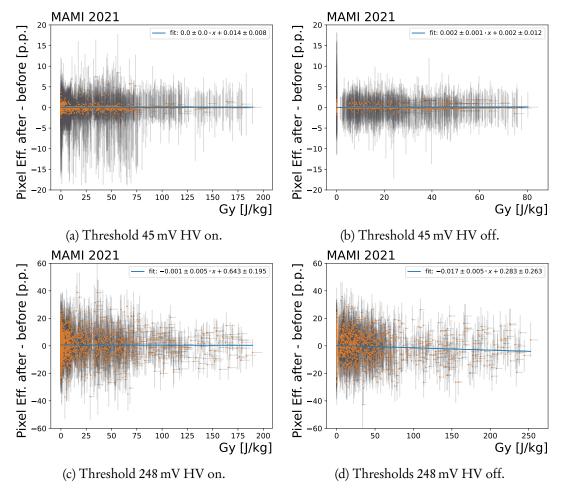

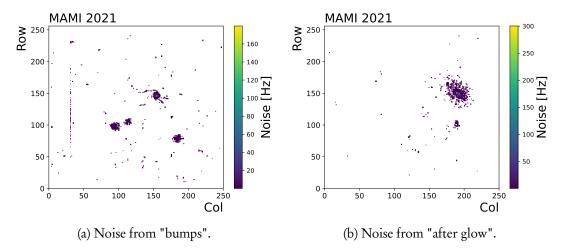

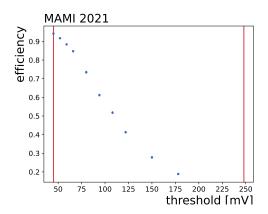

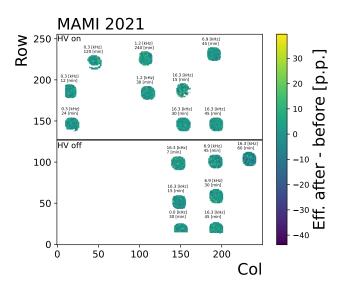

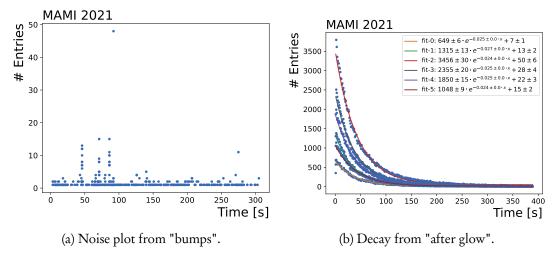

|    | 14.3 Irradiation results                          | 129 |

| 15 | Advanced muon spin spectroscopy using MuPix chips | 135 |

| 10 | 15.1 Background and introduction                  | 135 |

|    | 15.1.1 Muon beam at PSI                           | 136 |

|    | 15.1.2 Introduction to the $\mu$ SR technique     | 136 |

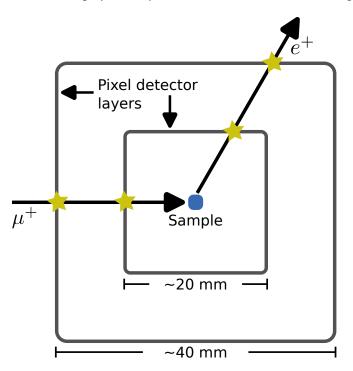

|    | 15.2 Conceptual design                            | 137 |

|    | 15.2.1 Current status                             | 138 |

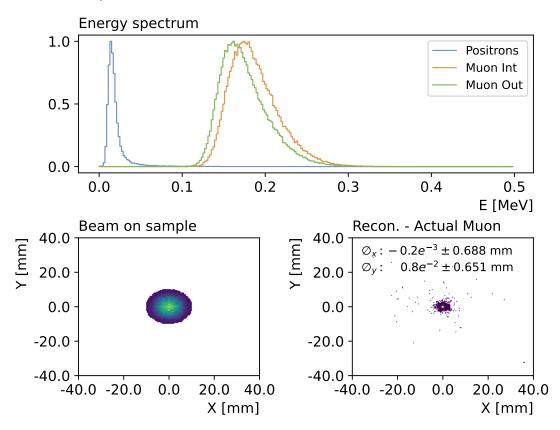

|    | 15.3 Monte-Carlo simulation                       | 139 |

|    | 15.4 Prototype and first beam tests               | 140 |

| V  | Conclusion and Outlook                            | 143 |

|    |                                                   |     |

| 16 | Conclusion and outlook                            | 145 |

| VI | Appendices                                        | 147 |

| A  | Acronyms                                          | 148 |

### CONTENTS

| В   | Add             | itional Material                | 152 |

|-----|-----------------|---------------------------------|-----|

|     | B.1             | The Mu3e Experiment             | 152 |

|     | B.2             | Switching Board                 | 154 |

|     | B.3             | First Detector Integration      | 155 |

|     | B.4             | Front-end Board Synchronisation | 156 |

|     | B.5             | Mu3e Integration Run 2021       | 157 |

|     | B.6             | MuPix Irradiation Studies       | 158 |

| С   | Pub             | lications                       | 160 |

| Lis | st of I         | Figures                         | 163 |

| Lis | st of T         | Tables                          | 167 |

| Bi  | Bibliography    |                                 |     |

| Ac  | Acknowledgement |                                 |     |

## Part I Introduction

The first chapter provides a theoretical introduction to lepton-flavour violation (LFV), followed by a brief explanation of the detector principles used in the Mu3e experiment. The part will conclude with a brief discussion of readout electronics and an introduction to field programmable gate arrays (FPGAs), which are the main building blocks of the Mu3e data acquisition (DAQ) system. Finally, an overview of the experimental setup of the Mu3e experiment will be given.

1

## Theory

Particle physics seeks to understand the fundamental laws of nature on a microscopic scale, and the results of this quest are encapsulated in the Standard Model of particle physics (SM). The SM is a relativistic quantum field theory (QFT), specifically a gauge theory with a  $U(1) \times SU(2) \times SU(3)$  symmetry, which describes nature in terms of elementary particles and their interactions.

In Section 1.1, a detailed discussion of the SM based on Griffiths [4] is provided. Due to its relevance to this thesis, muon ( $\mu$ ) decays in and beyond the SM are discussed in Section 1.2.1. The last part of the chapter (Section 1.3) gives an overview of different experiments that search for charged lepton-flavour violation (CLFV) decays.

### 1.1 The Standard Model of particle physics

The world we observe in our daily lives is constructed from a relatively small number of particles. Atoms serve as the fundamental building blocks of all stable matter on Earth. However, atoms themselves are not fundamental; they are composed of electrons, protons, and neutrons. Although electrons are elementary particles, protons and neutrons consist of quarks, specifically the up quark (u) and the down quark (d). Together with the electron neutrino, these particles form the first generation of spin-1/2 particles known as fermions. In high-energy interactions, additional generations of fermions emerge. In total, there are 12 fermions, each with its corresponding antiparticle, that possess the same mass but opposite quantum numbers. The difference between the three generations of fermions is caused by their mass and flavour quantum number, all the other properties are the same.

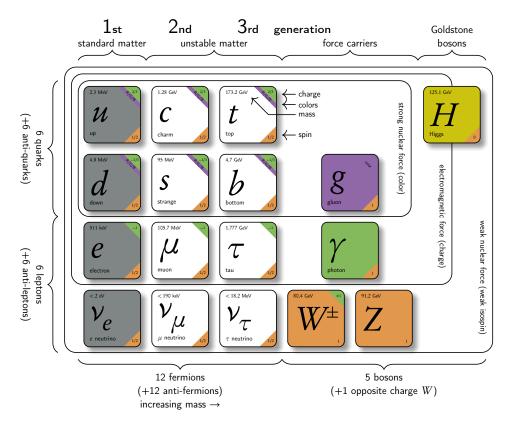

In the SM, every particle is considered a field, either a fermion or a boson field, as illustrated in Figure 1.1. The bosons consist of four kinds of vector bosons with spin 1 and a scalar boson with spin 0, known as the Higgs boson. While vector bosons mediate interactions between particles, the Higgs boson is a pseudo-Goldstone boson resulting from spontaneous symmetry breaking via the Higgs mechanism, which imparts mass to particles. The Higgs field is typically represented by a complex scalar doublet in the fundamental representation of SU(2). This doublet is often written as:

$$\phi = \begin{pmatrix} \phi^+ \\ \phi^0 \end{pmatrix} \tag{1.1}$$

Here,  $\phi^+$  and  $\phi^0$  are the charged and neutral components of the Higgs doublet, respectively. When the Higgs field acquires a vacuum expectation value (VEV), the SU(2) × U(1) symmetry is spontaneously broken, resulting in the generation of masses for the W and Z bosons as well as fermions through the Yukawa couplings with the Higgs field. SU(2) (or SU(2)<sub>L</sub>) is the symmetry group associated with weak isospin, and U(1) (or U(1)<sub>Y</sub>) is the symmetry group associated with hypercharge. The doublet structure allows for the generation of masses in a way that preserves gauge symmetry.

Figure 1.1: Overview of the building blocks of the SM, including the quarks, leptons, and force-carrying bosons, taken from [5].

As mentioned above, the SM describes interactions through four vector bosons, responsible for mediating fundamental forces. The strong interaction is mediated by eight gluons, while the weak interaction is carried out by two charged  $W^{\pm}$  bosons and a neutral Z boson. Electromagnetic interactions are mediated by the photon ( $\gamma$ ). Notably, gluons and the  $\gamma$  are massless, while  $W^{\pm}$  and Z bosons have masses of approximately 80.4 GeV/ $c^2$  and 91.2 GeV/ $c^2$ , respectively [6]. These boson fields arise from the local gauge invariance of the SM particle fields, as the SM follows a U(1) × SU(2) × SU(3) gauge theory. The strong interaction emerges due to the symmetry of local SU(3) transformations.

The SM successfully unifies the weak and electromagnetic forces into the electroweak interaction, including a neutral gauge boson [7]. The Weinberg-Salam theory in the SM describes this unification as a Yang-Mills field with a  $U(1) \times SU(2)$  gauge group. The Higgs mechanism spontaneously breaks the symmetry of  $U(1) \times SU(2)$  and imparts non-zero masses to the  $W^{\pm}$  and Z bosons [8]. This mechanism also predicts the existence of the Higgs boson, which was discovered at the Large Hadron Collider (LHC) in 2012 [1, 2]. Fermions also acquire mass through Yukawa interactions with the Higgs field.

The three generations of fermions in the SM are classified into quarks and leptons. Each generation of quarks consists of one quark with an electrical charge of q = 2/3 and one with q = -1/3. Subsequent

generations introduce heavier quarks, with the top quark (t) being particularly massive at approximately 173.2 GeV/c<sup>2</sup>, in contrast to the light up quark (u) with a mass of 2.3 MeV. All quarks interact through strong, weak, and electromagnetic forces because of their colour charge, weak isospin, and electric charge. Quarks can also mix with each other via the weak force. This mixing is described by the Cabibbo-Kobayashi-Maskawa (CKM) matrix [9]:

$$\begin{bmatrix} d' \\ s' \\ b' \end{bmatrix} = \begin{bmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{bmatrix} \begin{bmatrix} d \\ s \\ b \end{bmatrix}$$

(1.2)

On the left, the weak-interaction doublet partners of down-type quarks are shown. On the right, the CKM matrix is presented, accompanied by a vector depicting the mass eigenstates of the down-type quarks. The CKM matrix serves to characterise the likelihood of a transition from a flavour (i) quark to another flavour (j) quark. These transitions are directly proportional to the square magnitude of the corresponding matrix elements, denoted as  $|V_{ij}|^2$  [6].

Leptons are classified into three generations of electrically charged particles: electrons (e's), muons ( $\mu$ 's), and taus ( $\tau$ 's), and three generations of electrically neutral neutrinos: electron neutrino ( $\nu_e$ ), muon neutrino ( $\nu_\mu$ ), and tau neutrino ( $\nu_\tau$ ). It should be noted that neutrinos are assumed to be massless in the SM.

Historically, the muon was thought to be an excited state of the electron, suggesting that the decay  $\mu \to e\gamma$  should be possible [10]. However, this decay was not observed, leading to the introduction of a new quantum number, called the lepton number, which was assumed to be a conserved quantity [11].

While the SM can accurately describe physical processes up to the scale of electroweak interactions, it relies on the measurement of 19 free parameters. The best estimates of these values at the time of writing are summarised in Table 1.1. The mass of the Higgs boson is not protected from large quantum corrections in the SM, potentially leading to a much higher mass than observed in experiments, a challenge known as the hierarchy problem [4]. Furthermore, the gauge hierarchy problem arises due to the lack of gauge coupling unification at high energy scales in the SM, a feature expected in many theories beyond the SM.

In addition to the theoretical challenges discussed above, the SM faces compelling experimental anomalies. In particular, two observations cannot be explained within the confines of the SM. One such phenomenon is the nature of dark matter, which remains elusive despite constituting a substantial fraction, approximately 25 %, of the total matter content of the universe. This enigmatic substance coexists with the 5 % SM baryonic matter and the enigmatic 70 % attributed to dark energy. The existence of dark matter is inferred from its gravitational effects, prominently observed in phenomena such as the measured velocity distributions of stars orbiting within galaxies [12]. Despite rigorous investigations, the fundamental properties and interactions of dark matter particles remain shrouded in mystery. On the other hand, dark energy is driving the continuous acceleration of the expansion of the universe, while its origin is unknown.

Furthermore, the phenomenon of neutrino oscillations presents a significant challenge to the SM [13]. The SM is assuming massless neutrinos, leading to their flavour eigenstates being equivalent to their mass eigenstates. This equivalence leads to the conclusion that the lepton-flavour is conserved. Consequently, in the SM, the rates for decays such as  $\mu \to e \gamma$  or  $\mu^+ \to e^+ e^- e^+$  are zero.

However, experimental evidence has painted a different picture [14, 15, 16]. The neutrino oscillation,

observed by the neutrinos that transition between their different generations as they traverse space, signifies a key departure from the SM predictions. The observed neutrino oscillations are described by the Pontecorvo — Maki — Nakagawa — Sakata (PMNS) matrix [17, 18]. This discovery compels the recognition that neutrinos must possess non-zero masses, a revelation that has far-reaching implications for our understanding of particle physics and the nature of neutrinos themselves. Specifically, the observation of neutrino oscillations implies that the mass differences between the neutrinos must be non-zero, although the mass of the lightest neutrino could still be zero.

| #  | Symbol               | Description            | Value          |

|----|----------------------|------------------------|----------------|

| 1  | $m_e$                | Electron mass          | 0.511 MeV      |

| 2  | $m_{\mu}$            | Muon mass              | 105.7 MeV      |

| 3  | $m_{	au}^{'}$        | Tau mass               | 1.78 GeV       |

| 4  | $m_u$                | Up quark mass          | 1.9 MeV        |

| 5  | n 1 1                |                        | 4.4 MeV        |

| 6  | u                    |                        | 87 MeV         |

| 7  | $m_c$                | Charm quark mass       | 1.32 GeV       |

| 8  | $m_b$                | Bottom quark mass      | 4.24 GeV       |

| 9  | $m_t$                | Top quark mass         | 173.5 GeV      |

| 10 | $\theta_{12}$        | CKM 12-mixing angle    | 13.1°          |

| 11 | $\theta_{23}$        | CKM 23-mixing angle    | 2.4°           |

| 12 | $\theta_{13}$        | CKM 13-mixing angle    | 0.2°           |

| 13 | λ                    | CKM CP violation phase | 0.995          |

| 14 | $g_1$ or $g'$        | U(1) gauge coupling    | 0.357          |

| 15 | g <sub>2</sub> or g  | SU(2) gauge coupling   | 0.652          |

| 16 | g <sub>3</sub> or gs | SU(3) gauge coupling   | 1.221          |

| 17 | $	heta_{QCD}$        | QCD vacuum angle       | ~0             |

| 18 | v                    | Higgs VEV              | 246 GeV        |

| 19 | 19 $m_H$ Higgs mass  |                        | 125.09(24) GeV |

Table 1.1: List of the 19 free parameters of the SM, taken and adopted from [19].

Combining the SM with neutrino oscillations, the rate for  $\mu \to e \gamma$  or  $\mu^+ \to e^+ e^- e^+$  is no longer zero, but of the order of  $10^{-55}$  [20]. The challenges presented by the neutrino oscillation to the SM emphasise the need for new theoretical frameworks that can address these observations. Since there are only left-handed neutrinos in the SM, no interaction with the Higgs field is possible. Therefore, unlike other fermions, they cannot get their mass from the Higgs mechanism.

To address these issues, ongoing particle physics experiments actively seek deviations from SM predictions. A possibility of exploration is the search for CLFV decays, which violate the conservation of the lepton-flavour. An illustrative example of CLFV is the decay  $\mu^+ \to e^+e^-e^+$ , a process strictly forbidden in the SM. As mentioned above, it is even impossible to measure when extending the SM with neutrino oscillations. The detection of such a decay would serve as a clear indication of physics beyond the SM. The subsequent sections delve into a more detailed discussion of muon decays both within and beyond the SM.

### 1.2 Muon decays

To appreciate the significance of this decay, it is essential to provide context on  $\mu$  decays within both the SM and beyond it.

### 1.2.1 Muon decays in the Standard Model

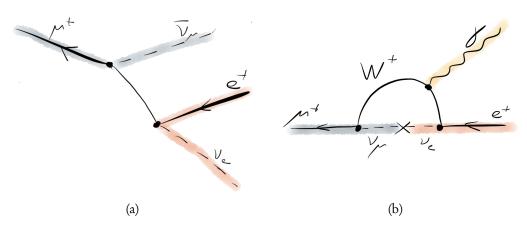

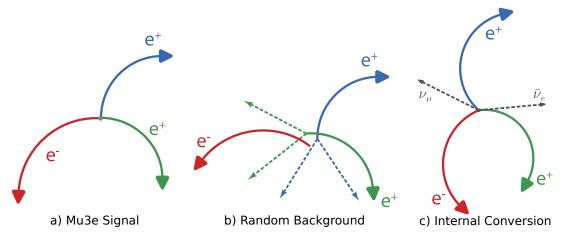

In the SM,  $\mu$  decay exclusively occurs through the weak interaction. The leading-order process is the Michel decay (see Figure 1.2a):

$$\mu^+ \to e^+ \nu_e \, \overline{\nu}_\mu. \tag{1.3}$$

Figure 1.2: In Figure 1.2a the Michel decay of the muon into an electron (e), an electron neutrino  $(v_e)$  and an anti muon neutrino  $(\bar{v}_{\mu})$  is shown. In Figure 1.2b the muon decay by the exchange of an  $v_e$  and  $v_{\mu}$  in the expansion of the SM with massive neutrinos is presented.

This process is mediated by the exchange of a virtual W boson. The branching fraction (BF) for this decay is close to 100 % [6]. The next-to-leading-order process is the radiative decay:

$$\mu^+ \to e^+ \nu_e \, \overline{\nu}_\mu \, \gamma. \tag{1.4}$$

For photon energies above 10 MeV, the BF is approximately 1.4(4) ×  $10^{-2}$  [21]. Additionally, in the radiative decay, the emitted  $\gamma$  can convert into an electron-positron pair, giving rise to the internal conversion decay:

$$\mu^+ \to e^+ e^- e^+ \nu_e \, \overline{\nu}_{\mu}.$$

(1.5)

This process has a BF of approximately  $3.4(4) \times 10^{-5}$  [6]. The decay  $\mu^+ \to e^+e^-e^+$  is strictly forbidden within the framework of the SM due to its violation of the conservation of the flavour of leptons. However, when the SM is extended to incorporate neutrino oscillations, as depicted in Figure 1.2b, this decay process can become possible. In this extended model with massive neutrinos, the BF for  $\mu^+ \to e^+e^-e^+$  is astonishingly minuscule, estimated to be on the order of  $10^{-55}$  [22]. This almost infinitesimal probability makes it exceedingly improbable that such a decay could be observed within any reasonable time frame.

### 1.2.2 Muon decays beyond the Standard Model

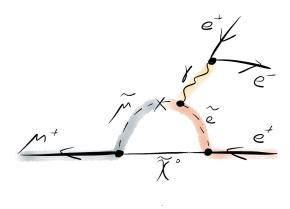

In the realm beyond the SM, there exist theoretical frameworks that predict the occurrence of CLFV decays at observable BFs. One class of such theories is supersymmetry (SUSY) [20], which posits the existence of superpartners for every known particle in the SM. These superpartners have different spin values compared to their SM particles. In particular, each fermion in the SM has a supersymmetric boson partner and vice versa. Although these superpartners have yet to be observed, their potential discovery holds promise for resolving some of the lingering questions in particle physics. Within the framework of SUSY, the decay  $\mu^+ \rightarrow e^+e^-e^+$  could materialise through a quantum loop involving SUSY particles, as illustrated in Figure 1.3 [23].

Figure 1.3:  $\mu$  decay via SUSY particles.

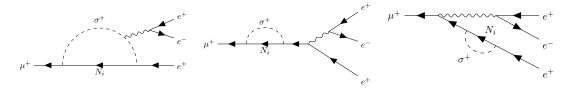

The Scotogenic Model, initially proposed by Ernest Ma in 2006 [24], is another theoretical framework designed to address two key puzzles in particle physics: neutrino mass generation and the identification of a dark-matter candidate, all while remaining consistent with the SM. This model extends the SM by introducing three right-handed neutrinos ( $N_i$ ) and a scalar  $SU(2)_L \times U(1)_Y$  doublet. Here, i represents the isospin, L the lepton number, and Y the hypercharge. For these right-handed neutrinos, the quantum numbers for hypercharge and isospin are zero. Note that so far only left-handed neutrinos and right-handed antineutrinos have been observed in nature. Through this extension, it achieves the generation of the SM neutrino masses via a radiative seesaw mechanism that does not necessitate the existence of very massive sterile neutrinos.

Figure 1.4: Possible production channels for the decay  $\mu^+ \to e^+ e^- e^+$  considering the Scotogenic Model (cf. [25]) by the loop of the scalar doublet  $\sigma^+$ .

A feature of the Scotogenic Model is the incorporation of sterile right-handed neutrinos  $(N_i)$ . These neutrinos, being sterile, have the potential to violate lepton-flavour conservation. Possible Feynman diagrams that illustrate how these sterile neutrinos  $(N_i)$  can contribute to CLFV in the context of decay  $\mu^+ \to e^+e^-e^+$  are depicted in Figure 1.4.

In addition to these theories, there exist numerous other theories in which the decay  $\mu^+ \to e^+e^-e^+$  may occur. For instance, in left-right symmetric models of the weak interaction, parity is conserved above the scale of symmetry breaking. This conservation leads to the existence of right-handed neutrinos and neutrino masses, among other phenomena. These models can be implemented using a Higgs triplet composed of a neutral scalar ( $\Delta^0$ ), a singly charged scalar ( $\Delta^+$ ), and a doubly charged scalar ( $\Delta^{++}$ ) [26, 27, 28, 29, 30, 31, 32, 33, 34, 35]. Consequently, the decay  $\mu^+ \to e^+e^-e^+$  can occur at the tree level. Furthermore, models that incorporate an extended gauge sector or extra dimensions introduce new heavy-vector bosons, such as Z' [36, 37, 38]. Through flavour-off-diagonal couplings, a Z' boson can mediate the decays  $\mu^+ \to e^+e^-e^+$ .

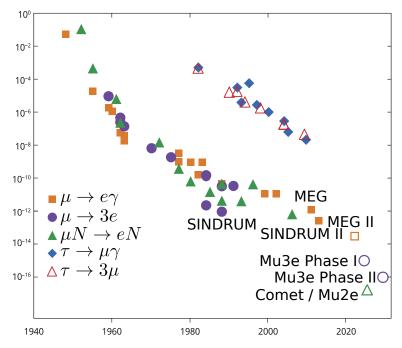

All the theoretical frameworks mentioned above are subject to stringent experimental constraints that restrict their predicted rates of CLFV decays. For instance, the combined Mu to E Gamma (MEG) and MEG II experiment have established the most stringent limit on the CLFV decay  $\mu^+ \to e^+ \gamma$ , reporting a BF of  $\mathcal{B}(\mu^+ \to e^+ \gamma) < 3.1 \times 10^{-13}$  at 90 % confidence level (CL) [39]. Similarly, the SINDRUM experiment has placed constraints on the CLFV decay  $\mu^+ \to e^+ e^- e^+$ , setting a BF limit of  $\mathcal{B}(\mu^+ \to e^+ e^- e^+) < 1.0 \times 10^{-12}$  at 90 % CL [40]. Furthermore, the SINDRUM II experiment has established limits on the CLFV process  $\mu^- \text{Au} \to e^- \text{Au}$  with a BF of  $\mathcal{B}(\mu^- \text{Au} \to e^- \text{Au}) < 7 \times 10^{-13}$  at 90 % CL [41]. In the next section, a more detailed overview of the MEG, MEG II and SINDRUM experiments is provided, based on the paper "Introduction to Charge Lepton-Flavour Violation" [42].

### 1.3 Charged lepton-flavour violation experiments

The search for CLFV processes is crucial in the quest to discover new physics beyond the SM, given the multitude of different theories that predict varying branching ratios for these processes. Numerous experiments have been conducted in the past to explore various CLFV decays, including rare  $\mu$  and  $\tau$  decays, as well as muon-to-electron conversion in nuclei.

Muon-based experiments have played a central role in these efforts due to several advantageous characteristics. Muons can be produced in substantial quantities, possess a relatively long lifetime of approximately 2.2  $\mu$ s, and exhibit purely leptonic decay modes. Currently, different experiments are being constructed and / or data is taken to search for different LFV decay modes of the  $\mu$ .

$\mu^+ \to e^+ \gamma$  is, an important process under investigation by the MEG (II) experiment [43, 44].  $\mu^+ N \to e^+ N$ , which is the focus of experiments such as COMET [45] and Mu2e [46]. Meanwhile, the Mu3e experiment, currently under construction, is specifically designed to investigate the decay mode  $\mu^+ \to e^+ e^- e^+$ .

All these experiments follow a common approach: muons interact or stop on a target, and the resulting decay particles are carefully measured. As mentioned above, the current limit for  $\mu^+ \to e^+e^-e^+$  was established by the SINDRUM experiment [40], and its detector concepts are discussed in this context. The diversity of these CLFV experiments and their associated processes allows for a comprehensive exploration of CLFV and the potential discovery of new phenomena in physics.

#### 1.3.1 SINDRUM

The most recent search for the  $\mu^+ \to e^+e^-e^+$  decay was carried out in 1988 by the SINDRUM experiment at the Paul Scherrer Institute (PSI). In this experiment, no events were observed within the signal region. Consequently, the researchers established an upper limit on the branching ratio

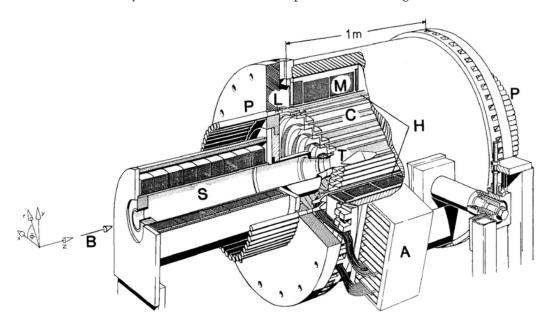

of  $\mathcal{B}(\mu^+ \to e^+ e^- e^+) < 1.0 \times 10^{-12}$  at 90 % CL [40]. The experimental setup used in SINDRUM is illustrated in Figure 1.5. The experiment involved stopping a muon beam at a rate of  $5 \times 10^6 \ \mu/s$  on a hollow double cone target. The resulting electrons were detected using five concentric multiwire proportional chambers, with three of them additionally equipped with cathode strips to determine the z coordinate. In addition, an array of scintillation counters was used to measure the timing information of the decay electrons. These detectors operated within a magnetic field of 0.33 T.

Figure 1.5: Sketch of the SINDRUM experiment, taken from [40]. B is the incoming muon beam, S is the beam transport solenoid, T is the muon stopping target, C is the low mass multiwire proportional chamber, H is cylindrical scintillator hodoscope, M is the magnatic coil, L are the light guides, A is the preamplifier and P are the photomultipliers.

Following its initial investigations, SINDRUM was reconfigured to explore neutrinoless  $\mu^- \to e^-$  conversion in muonic atoms. In this context, the experiment established a decay limit with a branching ratio of  $\mathcal{B} < 7 \times 10^{-13}$  at 90 % CL using gold as a target [41]. In contrast to the work presented in this thesis, the DAQ system of the SINDRUM and SINDRUM II experiments used a trigger system to read the detectors. To increase the limit set by the SINDRUM experiment, the DAQ system of a potential preprocessor experiment searching for  $\mu^+ \to e^- e^+ e^+$  needs to reconstruct all events online to be able to handle the increased accidental background.

### 1.3.2 MEG and MEG II

The most recent measurement of CLFV was conducted by the MEG and MEG II experiment, which searched for  $\mu^+ \to e^+ \gamma$ . The MEG experiment operated at PSI from 2009 to 2013, while the MEG II experiment is currently taking data. During the period 2009 to 2013, a total of 7.5 × 10<sup>14</sup> muons were stopped in the experiment. However, no excess events were detected, resulting in a new upper limit on this decay of  $\mathcal{B}(\mu^+ \to e^+ \gamma) < 4.2 \times 10^{-13}$  at 90 % CL [43].

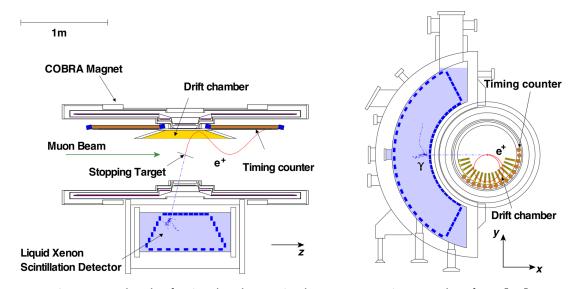

The MEG experiment used a unique setup: muons were stopped by a thin stopping target, consisting

of a single polyethylene sheet set at an angle of 70° to the beam, which maximised stopping efficiency while minimising multiple scattering and bremsstrahlung. Positrons resulting from muon decays were detected by a drift chamber system comprising 16 independent modules, covering angles from 191.25° to 378.75° [47]. The timing of the positrons was precisely measured using scintillating bars on the timing counters. Photons, integral to the objectives of the experiment, were detected by a liquid xenon calorimeter, specially designed to fully capture a 52.83 MeV photon shower. All components of the experiment, except the liquid xenon calorimeter, were located within a superconducting magnet that generated a field of approximately 1.27 T in the centre. To generate a gradient magnetic field, six coils with different radii are applied. In addition, two additional coils were used to compensate for the residual field around the liquid xenon calorimeter. The experimental setup is depicted in Figure 1.6.

Figure 1.6: Sketch of a simulated event in the MEG experiment, taken from [43].

The MEG experiment has undergone significant improvements that have led to a new experiment called MEG II [44]. These enhancements include the conversion of the drift chambers into a single cylindrical drift volume, improvements in the timing detector using scintillating tiles, replacing the photomultiplier tubes (PMTs) on the front face of the liquid xenon calorimeter with silicon photomultipliers (SiPMs) and the addition of a new radiative decay counter to suppress the background [44]. Resulting in a sensitivity of  $6 \times 10^{-14}$ , MEG II has been actively collecting data since 2021.

The MEG II experiment measured in 2021 a branching ratio limit of  $\mathcal{B}(\mu^+ \to e^+ \gamma) < 7.5 \times 10^{-13}$  at 90 % CL [48]. Both experiments have produced a combined branching ratio limit of  $\mathcal{B}(\mu^+ \to e^+ \gamma) < 3.1 \times 10^{-13}$  at 90 % CL. Again, in contrast to the work presented in this thesis, both the MEG and the MEG II experiments use a triggered DAQ system.

## Principles of Particle Detectors

In particle physics experiments, tracking detectors play a crucial role, as they enable the determination of both the momentum and direction of charged particles. The ideal tracking detector should minimise particle interaction, avoiding significant deflection, to reconstruct the particle's path accurately based on its interactions with the detector. This requires a minimal material budget.

In the Mu3e experiment, muons decay at rest, producing low-momentum electrons and positrons. Hence, minimising detector material is particularly vital to mitigate multiple-scattering effects, which become more pronounced at lower momenta. Advancements in semiconductor technology enable the construction of extremely thin detectors. In the following sections, the fundamentals of silicon detectors (Section 2.1), tracking systems (Section 2.2), and multiple scattering (Section 2.3), based on Thomson [49], will be explained.

Subsequently, the unique pixel detector employed in the Mu3e experiment will be explored (Section 2.4). Additionally, an introduction to scintillating detectors and an example using scintillating fibres in Section 2.5 will be given, with reference to Knoll's work [50]. Finally, the principles of the readout electronics used in the Mu3e experiment will be elucidated.

### 2.1 Silicon detectors

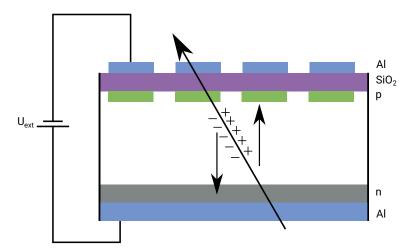

Figure 2.1: Sketch of a particle travelling through a silicon pixel detector. When an external voltage is applied, the whole area between the regions doped with p and n becomes active.

In Figure 2.1, a sketch of a silicon detector is provided. This detector comprises different regions doped with implants of type p or n, as well as  $n^+$  doped implants. P-type silicon can be achieved by implanting a phosphorous nucleus that has an extra electron. By doping with a boron nucleus, one can produce n-type silicon because boron has one electron less than silicon. When oppositely doped regions are joined, they form a pn-junction. Inside this junction, charge carriers have the ability to diffuse into the opposing region, where they recombine with their counterparts, resulting in the creation of a charge-free region around the pn-junction, known as the depletion zone. When an external reverse bias voltage is applied, the depletion zone expands and the detector can be depleted, allowing the entire volume to become active.

When a charged particle traverses the detector, it generates free electron-hole pairs. The application of voltage to the pn-junction enhances the motion of these particles towards the electric field, resulting in the generation of an induction signal that can be processed using amplifiers and comparators. Incorporation of small p-doped implants within the detector allows for precise measurement of spatial information. When these sensors are extended in one dimension, they are called strip detectors. If they possess fine segmentation in two dimensions, then they are known as pixel detectors.

### 2.2 Principle of tracking detectors

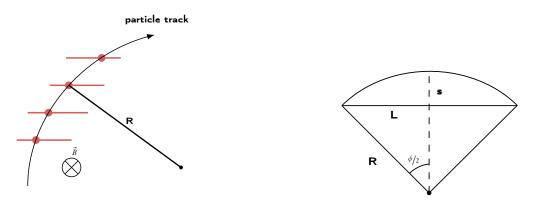

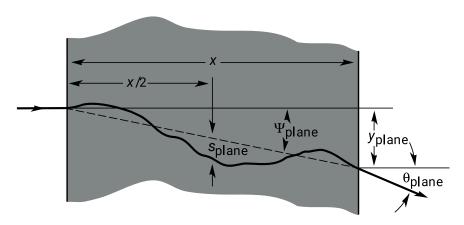

Figure 2.2: Sketch of a particle travelling through a tracking detector and important variables of the particle track in the x-y plane.

In Figure 2.2, a schematic representation of the trajectory of a particle is shown within a tracking detector, located in the x-y plane. To determine the momentum of a particle traversing a barrel-shaped tracking detector, one needs to apply a magnetic field perpendicular to the particle's path. Consequently, the Lorentz force equals the centripetal force, yielding the following momentum equation:

$$\frac{m \cdot v^2}{R} = e \cdot v \cdot B \to p = e \cdot B \cdot R. \tag{2.1}$$

Here, *m* denotes mass, *v* represents velocity, *e* signifies electric charge, and *p* stands for the particle's momentum. The variable *B* denotes the magnetic field applied perpendicular to the particle's track, and *R* represents the radius of the track (cyclotron radius). Note that the left part of this equation is only valid in non-relativistic scenarios. The tracking layer typically comprises multiple silicon

detectors. To assess the resolution of the momentum, the sagitta s is introduced, which can be derived for small  $\phi$  as follows (see right part of Figure 2.2:

$$s = R - R \cdot \cos\left(\frac{\phi}{2}\right) \approx R \cdot \frac{\phi^2}{8} = R \cdot \frac{L^2}{8 \cdot R^2}.$$

(2.2)

Furthermore, the momentum resolution is expressed as follows:

$$\frac{\Delta p}{p} = \frac{\Delta R}{R} = \frac{L^2}{8 \cdot R \cdot s} \cdot \frac{\Delta s}{s} \tag{2.3}$$

To achieve a superior momentum resolution, it is essential to have a long path (*L*), a strong magnetic field (*B*), and precise sagitta measurements. However, it is important to consider that in the Mu3e experiment, where the decay products possess lower momenta, multiple scattering effects must be taken into account. Furthermore, sagitta is not small in comparison to the radius in the case of the Mu3e experiment.

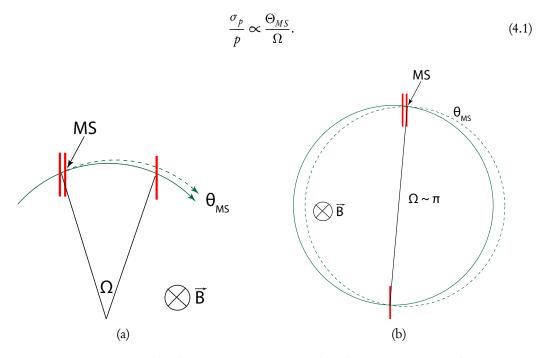

### 2.3 Multiple Scattering

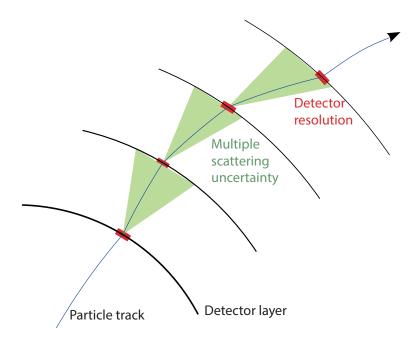

Figure 2.3: Particle passing through matter, taken from [6].

In Figure 2.3, the trajectory of a particle traversing matter is shown. The path of the particle is altered because of scattering interactions with the Coulomb fields of nuclei, leading to an offset from its original course and an alteration in its angle. When the detector is extremely thin, the offset can be ignored, focusing solely on the change in angle. The root mean square (RMS) of this angle, denoted as  $\Theta_{MS}$ , is accurately approximated by the Highland equation [6]:

$$\Theta_{MS} = \frac{13.6 \,\text{MeV}}{p \,\beta c} q \sqrt{\frac{x}{X_0}} \left[ 1 + 0.038 \log \left( \frac{x}{X_0} \right) \right]. \tag{2.4}$$

Here, p represents momentum,  $\beta c$  signifies the velocity of a particle with a charge q in units of electron charge, x is the path length within the material, and  $X_0$  is the radiation length of the material. Given that the electron has a fixed charge, the only parameter in the equation that can be modified is the radiation length, x. To achieve a precise momentum resolution, it is imperative to minimise the magnitude of the multiple scattering angle, imposing stringent constraints on the material budget.

Figure 2.4: Tracking in the scattering dominated regime, taken from [51].

As Equation 2.4 implies, the deviation is more pronounced for particles with lower momenta and for thicker detector layers. In the context of Mu3e, where particle momenta are in the range of a few tens of MeV, minimising material within the active detector volume is paramount for accurate momentum measurements. Apart from multiple scattering, the spatial uncertainty of individual measurement points along the track also contributes to momentum resolution as discussed above. Figure 2.4 illustrates that these spatial uncertainties can be disregarded when they are significantly smaller than the uncertainties introduced by scattering.

### 2.4 High Voltage Monolithic Active Pixel Sensors

In Section 2.1, the fundamental principles of silicon detectors were discussed. To extract the signal from these detectors, an amplification circuit can be integrated into the pixels, resulting in Active Pixel Sensors (APS). Alternatively, the entire signal readout can be placed on the chip, leading to Monolithic Active Pixel Sensors (MAPS). These chips cannot be fully depleted, as the required voltage would interfere with the circuits. Thus, they collect the signal via diffusion, which has the disadvantage of a relatively long charge collection time, typically on the order of microseconds, compared to the typical drift time in a bias field of the order of nanoseconds.

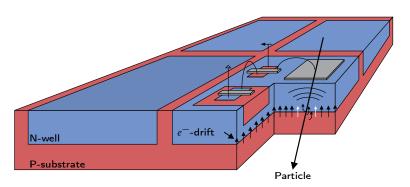

In Figure 2.5, a schematic of a High-Voltage Monolithic Active Pixel Sensor (HV-MAPS) is shown [52]. These sensors combine the monolithic characteristics of MAPS with the fast charge collection capability achieved by drift. This is accomplished by using a deep n-well located in the p-substrate, which forms a diode. Pixel electronics can be implemented inside the n-well where they are isolated from the depletion voltage. Due to the use of the deep n-well a high reverse bias voltage can be applied to the substrate, creating a large depletion zone. These deep n-wells are available in commercial high voltage (HV) complementary metal-oxide-semiconductor (CMOS) processes.

Figure 2.5: Sketch of a HV-MAPS sensor [52].

Furthermore, the sensor can be thinned from the back. This technology enables fast charge collection and guarantees a low material budget, ensuring good momentum resolution. The HV-MAPS pixel sensor used in the Mu3e experiment is called MuPix and in Section 4.3, a more specific discussion will give detailed explanations regarding this sensor.

### 2.5 Scintillating detectors

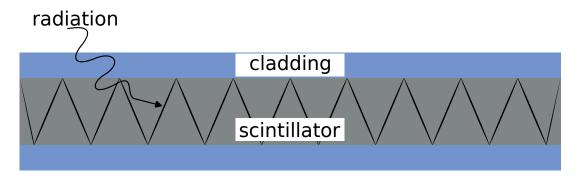

Scintillators are materials that produce light when they come into contact with ionising radiation. They come in different types and forms. For example, organic scintillators are made up of an activator and a surrounding material. When ionising radiation interacts with these scintillators, the energy of the particles is transformed into light through a fluorescence process that occurs within the activator material. In the case of a plastic scintillator, the main source of fluorescence, known as a fluor, is embedded within a solid polymer matrix called the base.

Figure 2.6: Sketch of light travelling inside a fibre scintillator.

One potential detector design involves shaping these plastic scintillators into fine fibres, capable of efficiently transporting emitted light over considerable distances through total internal reflection. This configuration is shown in Figure 2.6. In this setup, the scintillator is located in the core of the fibre, which is surrounded by a cladding material. The light produced within the core reaches the core-cladding boundary, potentially at an angle that exceeds the critical angle for total reflection. This allows light to propagate along the fibre. At the termination points of the fibres, photomultipliers can be integrated to enhance the signal. Photomultipliers achieve this by initially converting the incoming photons into electrons that are subsequently amplified.

## Readout Electronics

To enable the readout of various detectors within a particle physics experiment, a set of essential readout electronics must be in place. In the subsequent sections, the fundamental concepts underlying these components are explained. First, the intricacies of FPGAs, which serve as the primary building blocks in contemporary DAQ systems, will be explored. Following this, the principles of data transmission and the implementation of transceivers utilised within FPGAs will be explored. Lastly, an overview of the principles governing Peripheral Component Interconnect Express (PCIe), a commonly used interface in readout systems, will be provided. These sections are based on previous work by the author [53].

### 3.1 Field Programmable Gate Arrays (FPGAs)

FPGAs represent integrated circuits endowed with reprogrammable hardware capabilities. These devices enable users to modify their functionality after manufacturing using reconfigurable interconnect lines and Logic Elements (LEs). These LEs are constructed from Look-Up Tables (LUTs) and registers, with interconnect lines located between them.

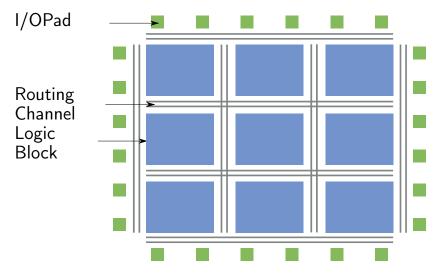

Figure 3.1: Structure of an FPGA.

In the context of this work, the hardware description language Very High Speed Integrated Circuit Hardware Description Language (VHDL) is harnessed to programme the FPGAs. Figure 3.1 offers a simplified depiction of a FPGA. This architectural marvel comprises a core consisting of LEs

interconnected through a global routing network, surrounded by a perimeter of input/output (I/O) pads. Additionally, FPGAs offer the option of using memory blocks and Hard Intellectual Property Core (IP) cores, which are predefined blocks within the device, thoughtfully designed and provided by the FPGA manufacturer. These IP cores are customised for specific tasks, such as high-speed serialisation or deserialisation.

With the aid of VHDL, the data flow and logic of the FPGA can be programmed. Initially, this design undergoes synthesis, resulting in the generation of a netlist. Subsequently, the fitting tool maps this netlist to the LEs and interconnects within the FPGA. In particular, this process takes into account the desired operating frequency. Ultimately, a configuration file is prepared for upload to the device. In the case of Intel (formerly Altera) FPGAs, this entire procedure is executed within the Intel Quartus Prime software [54].

### Logic Elements

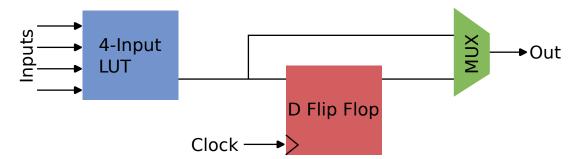

In Figure 3.2, an illustration of a LE with four inputs and one output is presented. The output can be connected directly to a LUT or driven by a flip-flop. A LUT is essentially a straightforward array that contains values that can be accessed by simple index operations. On the other hand, a flip-flop serves the purpose of information storage. Specifically, the D-flip-flop delivers data to the output when a clock edge is detected on the clock input. In the absence of a clock signal, changes in the input do not affect the output, leading to the retention of information within the flip-flop until a clock signal is detected. By routing multiple LUTs together, various Boolean functions can be effectively expressed.

Figure 3.2: Illustration of a simple LE containing a four input LUT and a D-flip-flop.

The FPGAs utilised in the Mu3e experiment belong to the category of Static Random Access Memory (SRAM)-based FPGAs. These FPGAs store the configuration of the LUT within SRAM cells. Furthermore, Intel FPGAs have been chosen for their favourable balance between fast and slow I/O, a sufficient quantity of LEs, and the availability of evaluation boards, some of which can be adapted for use in the final detector setup.

#### Routing

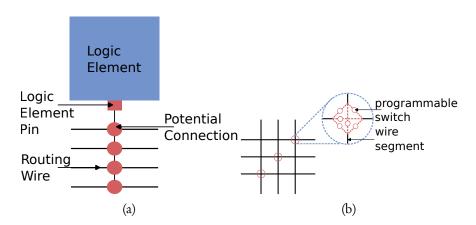

To establish connections between different LEs, input and output pins can be connected to the routing wires. Figure 3.3a provides an illustration of such a connection. Each of these routing wires extends to a switch box positioned at the intersections. Figure 3.3b presents these switch boxes, which are programmable to facilitate the interconnection of multiple LEs.

Figure 3.3: Figure 3.3a does show the connection of a LE to a routing wire. Figure 3.3b shows a sketch of a programmable switch sitting on the intersections of different routing wires.

### 3.2 Data Transmission in FPGAs

In the pursuit of identifying rare events, the study of numerous decays becomes imperative. Consequently, an immense volume of data requires processing. To accommodate such a data rate, high-speed data links and FPGAs capable of real-time data analysis are indispensable.

In this chapter, the fundamentals of data transmission are elucidated in Section 3.3. Subsequently, Section 3.4 delves into electrical data transmission, while Section 3.5 explores the concept of serial data links. Furthermore, the general implementation of high-speed data transmission and the intricacies of transmission within FPGAs will be discussed in Section 3.6. Optical data transmission is covered in Section 3.7. Finally, Section 3.8 describes a test procedure for assessing the performance of such data links followed by the basics of Peripheral Component Interconnect Express (PCIe) and Direct Memory Access (DMA). The key content and images in these sections have been sourced from references such as [55], [56], and [53].

### 3.3 Basics of data transmission

#### Electrodynamics

In the field of electrodynamics, the fundamental theory that underpins electrical and optical data transmission is based on classical electrodynamics, as originally formulated by Maxwell. This theory can be succinctly summarised through four key equations:

1. Gauss's Law for Electric Fields:

$$\vec{\nabla} \cdot \vec{D} = \rho \tag{3.1}$$

2. Faraday's Law of Electromagnetic Induction:

$$\vec{\nabla} \times \vec{H} - \frac{\partial \vec{D}}{\partial t} = \vec{j} \tag{3.2}$$

3. Faraday's Law of Magnetic Fields:

$$\vec{\nabla} \times \vec{E} + \frac{\partial \vec{B}}{\partial t} = 0 \tag{3.3}$$

4. Gauss's Law for Magnetic Fields:

$$\vec{\nabla} \cdot \vec{B} = 0 \tag{3.4}$$

Here,  $\vec{E}$  represents the electric field,  $\vec{B}$  the magnetic field,  $\vec{D}$  the electric displacement,  $\vec{H}$  the magnetising field,  $\rho$  the charge density and  $\vec{j}$  the current density. These equations describe the fundamental principles that govern electromagnetic phenomena. Additionally, there are relationships between these fields:

$$\vec{D} = \epsilon_r \epsilon_0 \vec{E} \tag{3.5}$$

$$\vec{B} = \mu_r \mu_0 \vec{H} \tag{3.6}$$

Here,  $\epsilon_0$  is the vacuum permittivity,  $\mu_0$  is the vacuum permeability,  $\epsilon_r$  and  $\mu_r$  are the corresponding values depending on the medium. Furthermore, the conductivity  $\sigma$  is determined by Ohm's law:

$$\vec{j} = \sigma \vec{E}. \tag{3.7}$$

#### Plane Waves in Materials

Following the calculations of [57], the behaviour of electromagnetic waves in different materials will be examined. Specifically, the wave equations governing their propagation in non-conducting and conducting media will be investigated in the following. In a non-conducting material (where conductivity,  $\sigma$ , and current density, j, are both zero), the wave equation takes the form:

$$\vec{\nabla}\vec{E} = \epsilon \mu \frac{\partial^2 \vec{E}}{\partial t^2}.$$

(3.8)

In a conducting medium (with  $\sigma$  and  $\vec{j} \neq 0$ ), the wave equation becomes:

$$\vec{\nabla}\vec{E} = \epsilon \mu \frac{\partial^2 \vec{E}}{\partial t^2} + \sigma \mu \frac{\partial \vec{E}}{\partial t}.$$

(3.9)

By introducing an ansatz for the electric field  $\vec{E}$  being a plane wave, one obtains:

$$\vec{E}(x,t) = \vec{E}_0 e^{i\omega t - ikx},\tag{3.10}$$

leading to:

$$k^2 = -i\omega\mu\sigma + \omega^2\mu\epsilon. \tag{3.11}$$

One then expresses the wave vector  $\vec{k}$  as the sum of real and imaginary parts:

$$\vec{k} = \alpha - i\beta, \tag{3.12}$$

yielding the solution for the plane wave as:

$$\vec{E}(x,t) = \vec{E}_0 e^{i\omega t - \alpha x} e^{\beta x}.$$

(3.13)

Here,  $\alpha$  determines the wave's length, and  $\beta$  represents the attenuation factor. The dispersion relation connecting the wave vector and frequency is given by:

$$k^2 = \omega^2 \mu \epsilon. \tag{3.14}$$

Solving for  $\alpha$  and  $\beta$ , one finds:

$$\alpha = \omega \sqrt{\mu \epsilon} \left( \frac{1}{2} + \frac{1}{2} \sqrt{1 + \frac{\sigma^2}{\omega^2 \epsilon^2}} \right)^{\frac{1}{2}}, \tag{3.15}$$

$$\beta = \frac{\omega \mu \sigma}{2\alpha}.\tag{3.16}$$

This analysis also applies to real dielectric materials where  $\epsilon$  is a complex number, leading to dispersion and attenuation equations with modified terms.

### Dielectrics in High-Speed Data Links

In high-speed electrical data links, dielectric materials play a critical role in reducing power loss. The power loss inside the dielectric is proportional to:

$$P_{\rm loss} \propto \omega \cdot \tan \delta$$

, (3.17)

where  $\tan \delta$  represents the loss tangent:

$$\tan \delta = \frac{\sigma + \omega \epsilon''}{\omega \epsilon'}.$$

(3.18)

The critical frequency,  $\omega_n$ , which delineates conducting and insulating modes within a material, is given by:

$$\omega_n = \frac{\sigma}{\epsilon}.\tag{3.19}$$

For many good insulators, conductivity is roughly proportional to frequency. Consequently, dielectric losses significantly impact high-speed data transmission in electrical links.

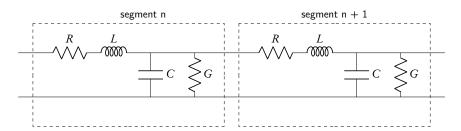

### 3.4 Electrical data transmission and Telegrapher's Equations

In the context of high-speed data transmission, electrical links play a crucial role. By modelling an electrical transmission line as an infinite cascade set of two-port systems, it is possible to derive the telegrapher's equations. These systems are constructed from segments with a series impedance (Z), which consists of a resistance (R) and an inductance (L), as well as a parallel admittance (y). The admittance is connected to the ground and is composed of a capacitance (C) and a shunt conductance (G). This configuration is illustrated in Figure 3.4. With the telegrapher's equation, it is possible to determine the wave impedance  $(Z_0)$ , which is given by:

$$Z_0 = \sqrt{\frac{R + i\omega L}{G + i\omega C}}. (3.20)$$

In the case of a lossless line (i.e., R = G = 0), the wave impedance ( $Z_0$ ) is independent of the frequency ( $\omega$ ).

Figure 3.4: Infinite Cascade model for deriving the telegrapher's equation, taken from [58].

However, in real-world transmission lines, resistance (R) and conductance (G) are non-zero. There are several reasons for this, including dielectric losses and the skin effect. The coefficient  $\beta$  determines the distance a wave travels within a conductor. The inverse of  $\beta$  is known as the depth of the skin  $(\delta)$ , which represents the distance over which the amplitude of the wave is reduced by a factor of 1/e. This skin effect restricts the area over which a high-speed wave can travel inside a conductor to its outer surface. Consequently, these effects can cause attenuation and dispersion of high-speed data signals, leading to inter-symbol interference.

To ensure successful high-speed data transmission, it is essential to address and correct these effects. The following section explores serial data links in more detail.

### 3.5 Serial data links for Inter-device Communication

Efficient communication between devices situated on different circuit boards often requires reducing the number of connectors on the boards. Serial data links offer a solution to this challenge by requiring only one line for communication, as opposed to the multiple lines used by parallel buses. However, serial data links must operate at higher frequencies than parallel buses to transmit the same volume of data.

Typically, high-speed data links are constructed using multiple layers, each serving a specific purpose. At a minimum, these links include the physical layer (PHY) and the data link layer. The PHY is responsible for mapping information to physical observables and facilitating the transfer of data to the data link layer. It also ensures electrical compatibility between devices, a crucial aspect of successful communication.

The data link layer plays a vital role in ensuring reliable data transmission and improving signal integrity. It accomplishes this by encoding data, aligning them for proper transmission, and performing clock recovery when necessary. These measures are essential for maintaining the integrity of the data being transmitted.

Beyond these foundational layers, additional layers can be added for error correction or to support protocol-dependent features. These additional layers are essential to address specific communication requirements and ensure the robustness of the data transfer process. In the following sections, the physical and data link layers of high-speed data links will be further explored and discussed in detail.

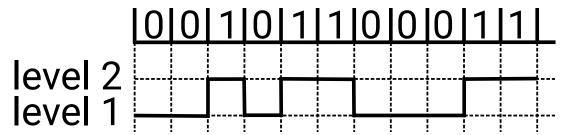

#### Physical Layer and non-return-to-zero Coding

In the context of electrical communication, data need to be translated into physical observables. Most often, electrical links use two voltage levels to represent the logical states "1" and "0" This is achieved through non-return-to-zero (NRZ) binary coding, which is a common technique for encoding data for transmission.

Figure 3.5: Illustration of the NRZ code for data transmission.

Figure 3.5 provides an illustration of the NRZ code, showing the two voltage levels applied to the cable to encode 1 and 0 states. High-speed links often implement this encoding using a differential signal with low common mode. One standard for implementing this technology is low-voltage differential signaling (LVDS) [59]. In Intel FPGAs, a proprietary standard called pseudo current mode logic (PCML) [60] is used for very high-speed links, typically in the range of gigabits per second.

To facilitate data transmission, a fast clock is used to serialise the data on the transmitter side. This clock must also be recovered on the receiver side to accurately capture the bits. For clock recovery, a circuit known as a Clock and Data Recovery (CDR) system is used, which typically includes phase interpolation and phase-locked loops (PLLs). Additionally, there are methods where the clock is transferred from the transmitter, and the data is recovered using this clock. In the Mu3e experiment, the second option was chosen.

### Phase-Locked Loops

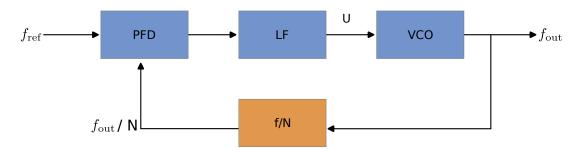

A PLL is a crucial component in clock and data recovery. It generates an output signal whose phase is related to the phase of an input signal. Figure 3.6 illustrates the basic principle of a PLL.

The operation of a PLL involves the following components:

- 1. **phase frequency detector** (PFD): It compares the phase of the input signal (reference frequency) with the phase of the feedback signal (output frequency divided by an integer N) and generates a control voltage (U) based on their phase difference.

- 2. **loop filter** (LF): The control voltage (U) passes through a LF, which smooths out rapid changes and generates a voltage that adjusts the voltage controlled oscillator (VCO).

- 3. **voltage controlled oscillator** (VCO): The VCO generates the output frequency  $(f_{\text{out}})$  based on the adjusted control voltage. The VCO frequency is controlled by the control voltage.

- 4. **frequency divider (N)**: The output frequency is divided by an integer value N, which determines the final output frequency  $(f_{out})$ .

In steady state, the PLL generates an output frequency of  $f_{\text{out}} = f_{\text{ref}} \cdot N$ . The value of N, which is an integer, allows  $f_{\text{out}}$  to be changed only in the steps of  $f_{\text{ref}}$ . This limitation can result in very small

Figure 3.6: Illustration of the principle of a PLL.

reference frequencies ( $f_{\rm ref}$ ) if fine-grained adjustments are needed for  $f_{\rm out}$ . A possible approach to this problem involves the incorporation of a divider between  $f_{\rm ref}$  and the PFD. Since the frequency divider on the feedback path divides by N and the reference input divider divides by M, the PLL is able to multiply  $f_{\rm ref}$  by  $\frac{N}{M}$ .

#### Data Link Layer and Encoding Schemes

The data link layer plays a critical role in data transmission by encoding data and managing data protocols, following [61, 58]. Several encoding schemes are commonly used in high-speed data links, including 8b/10b, 64b/66b, and 128b/130b. In this section, the focus is on the 8b/10b encoding scheme and its key features. The 8b/10b encoding scheme [62] converts 8 bits of user data to 10 bits for transmission on the communication line. This conversion allows for the exclusion of some possible 1024-bit patterns, which imposes a run-length limit of five consecutive equal bits. Additionally, the disparity, defined as the sum of one and zero in a word, should not exceed two in this encoding scheme. By implementing these constraints and decoding some 256 possible 8-bit words in two different ways, the bit sequence is designed to contain an equal number of ones and zeros, ensuring direct current (DC) balancing. Furthermore, the running disparity (RD) is continuously measured in the data stream and can only have values of  $\pm 1$ .

| Previous RD   | Next RD    | Disparity choices | Disparity chosen |

|---------------|------------|-------------------|------------------|

| <del>-1</del> | -1         | 0                 | 0                |

| <b>—</b> 1    | +1         | $\pm 2$           | +2               |

| +1            | +1         | 0                 | 0                |

| +1            | <b>—</b> 1 | $\pm 2$           | <b>—2</b>        |

Table 3.1: Choice of disparity, taken from [63].

This mechanism helps to keep the disparity within the limits specified in Table 3.1. Moreover, the use of the 8b/10b encoding enables the detection of errors caused by a single bit flip.

#### Control Symbols and DC Balance

In the 8b/10b encoding, there are special control symbols, as detailed in Table 3.2. Among these symbols, K.28.1, K.28.5, and K.28.7 are referred to as "comma symbols". These comma symbols are used to identify word boundaries (finding the alignment of the 8b/10b codes within a bit stream), helping the receiver correctly interpret the data.

|          | 8 bit | 10 bit      | 10 bit      |

|----------|-------|-------------|-------------|

| Name     | HEX   | RD = -1     | RD = +1     |

| K.28.0   | 1C    | 001111 0100 | 110000 1011 |

| K.28.1 † | 3C    | 001111 1001 | 110000 0110 |

| K.28.2   | 5C    | 001111 0101 | 110000 1010 |

| K.28.3   | 7C    | 001111 0011 | 110000 1100 |

| K.28.4   | 9C    | 001111 0010 | 110000 1101 |

| K.28.5 † | BC    | 001111 1010 | 110000 0101 |

| K.28.6   | DC    | 001111 0110 | 110000 1001 |

| K.28.7 † | FC    | 001111 1000 | 110000 0111 |

| K.23.7   | F7    | 111010 1000 | 000101 0111 |

| K.27.7   | FB    | 110110 1000 | 001001 0111 |

| K.29.7   | FD    | 101110 1000 | 010001 0111 |

| K.30.7   | FE    | 011110 1000 | 100001 0111 |

Table 3.2: List of all control symbols in 8b/10b encoding. All symbols with † are called comma symbols and they are used to align the 8b/10b data stream. The bit order is from the least significant bit to the most significant bit taken from [63].

#### 3.6 High speed links in FPGAs

In this section, the concept of a high-speed link is implemented in an FPGA, focussing on the example of the Intel Arria 10 FPGA, which is a key component in this thesis. Specifically, the examination of the Arria 10 GX Device Transceiver (TX) and the Intel Arria 10 TX PHY. The information provided here is based on the Intel Arria 10 TX PHY User Guide [64].

#### **GX** Transceiver

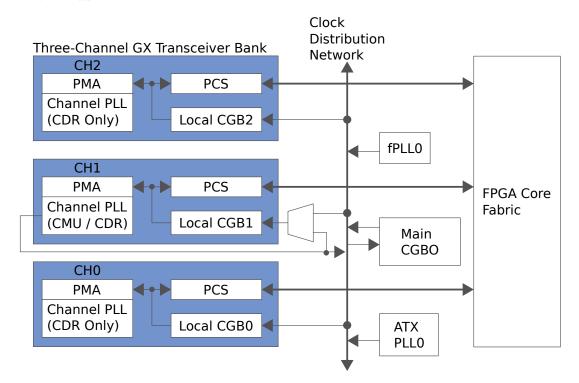

The Intel Arria 10 FPGA is equipped with a substantial number of GX TX channels, with the capability to handle high-speed digital signals and CDR. Each of these channels can transmit data at speeds up to 17.4 Gbps. These channels are organised into banks with up to eight TX in each bank. These banks are strategically placed in the left and right periphery of the FPGA device. In Figure 3.7, an example of one such TX bank containing three channels can be seen.

The overall clock distribution to the three channels is done via the main clock generation block (CGB). Each channel has integrated features, including a PLL and a local CGB. The local CGB divides and distributes the clock to the Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) blocks. This is done in non-bonded configuration mode, where the channels are not related to each other. In this mode, the feedback path is local to the PLL.

The PCS plays a crucial role in encoding, decoding, and management of alignment markers within the data stream. Alignment is necessary because the TXs lack knowledge about the word boundaries within the stream. The PCS serves as an interface between the PMA and the FPGA Core Fabric. Additionally, each channel is connected to the Clock Distribution Network and the FPGA Core Fabric. The FPGA features fractional PLLs (fPLLs) that can generate lower clock frequencies, especially for data rates below 12.5 Gbps. There are also Advanced Transmit PLLs (ATXs) that cover the entire

range of supported data rates.

Figure 3.7: High level overview of the TX bank architecture of a bank made out of 3 TX channels, adopted from [64].

One notable advantage of the fPLLs is their ability to generate frequencies that are a rational fraction N/M of the reference frequency. This is achieved by first multiplying the reference frequency by an integer before feeding it into the PFD. In the context of the Mu3e experiment, all TX PLLs use the global 125 MHz clocks, provided by the clock and reset system (as discussed in Section 5.2), are their reference clocks. Since the Front-end board (FEB)<sup>1</sup> TXs operate at a data rate of 6250 Mbps, and the data packages are divided into 32-bit sections with 8b/10b encoding, the transceiver clock must be precisely 156.25 MHz. The use of fPLLs facilitates the achievement of this specific clock frequency requirement.

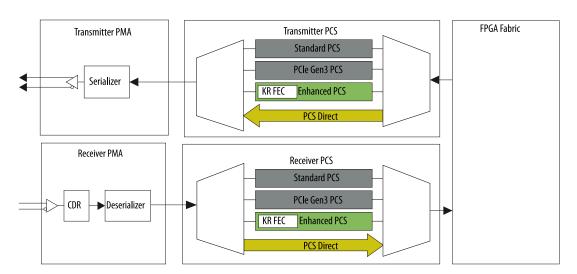

#### Intel Arria 10 Transceiver PHY Layer

The Intel Arria 10 TX PHY layer is designed to handle both the PMA and the PCS functions. The PMA serves as the electrical interface to the physical medium and incorporates various essential components, including serializer or deserializer (SERDES), clock and data recovery PLLs, transmit drivers for the analogue front end, and receive buffers for the analogue front end.

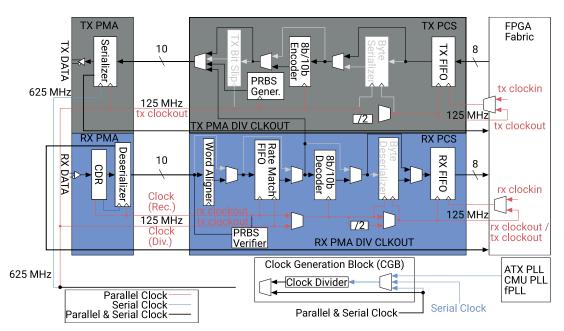

Figure 3.8 illustrates a duplex-mode TX channel. In this setup, three types of PCS are available to manage data at different rates. Table 3.3 provides information about the supported PCS types and their corresponding data rates.

<sup>&</sup>lt;sup>1</sup>More information about the FEB will be given in Chapter 6.

Figure 3.8: High level overview of a TX channel with a transmitter and a receiver part, taken from [64].

Additionally, one of the available PCS options is the use of a PCIe IP core, as referenced in [65]. PCIe is a high-speed serial bus interface commonly used to connect peripheral devices with the Central Processing Unit (CPU) in a personal computer (PC). The electrical standard and protocol of PCIe will be discussed later in Section 3.9.

| PCS type      | data rate                  |

|---------------|----------------------------|

| Standard PCS  | 1.0 Gbps to 10.813 44 Gbps |

| Enhanced PCS  | 1.0 Gbps to 17.4 Gbps      |

| PCIe Gen3 PCS | 8.0 Gbps                   |

Table 3.3: Supported PCS types.

#### Transceiver design IP blocks

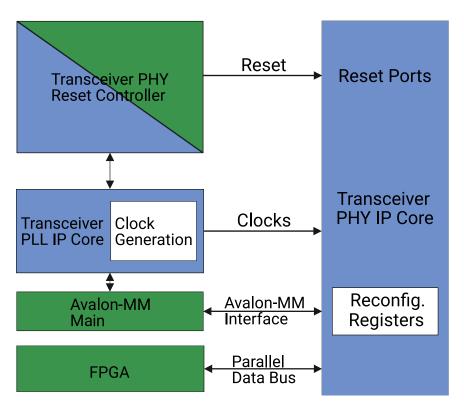

Figure 3.9 provides an overview of the fundamental building blocks comprising an Intel Arria 10 TX. Each TX PHY IP Core is equipped with reset ports and reconfiguration registers, as well as controls for configuring the PCS and PMA settings.

The reset ports are connected to a TX PHY Reset Controller IP Core, which serves the purpose of resetting individual channels within the TX PHY IP Core. This IP Core monitors the status of the TX PLL IP Core and triggers a reset if PLL fails to lock onto an input clock signal. The PLL, in turn, generates a clock signal that is supplied to the TX PHY IP Core.

Furthermore, an option for an Avalon Memory Mapped Interface Main (Avalon-MM) interface is available. This interface allows for the reading and writing of reconfiguration registers within the TX PHY IP Core. In the context of the Mu3e experiment, this option is used to monitor the current status of the TXs during operation.

Figure 3.9: Fundamental building blocks of an Intel Arria 10 TX. The blue blocks are generated by Quartus the green blocks can be generated by the user, taken from [64].

#### Transceiver Channel datapath and clocking

In Figure 3.10, the datapath and clocking configuration of a TX operating at a data rate of 1250 Mbps is illustrated. A similar type of TX is used in the Mu3e experiment to facilitate the distribution of the reset protocol, as discussed in Section 5.2. It is worth noting that all other TXs utilised in this study differ solely in their data rate and parallel data width.

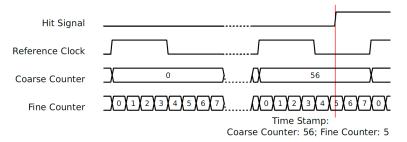

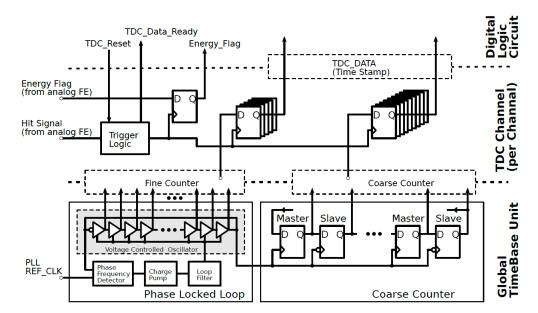

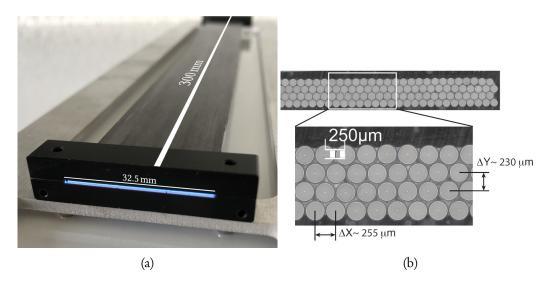

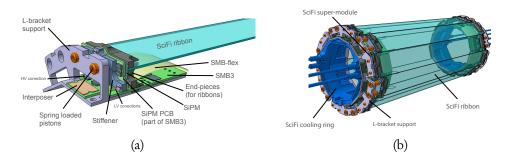

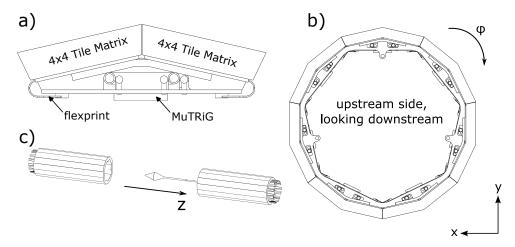

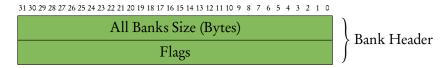

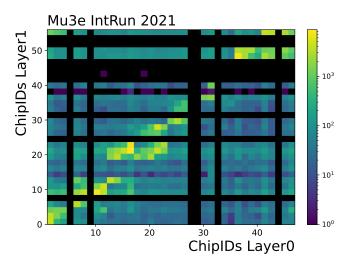

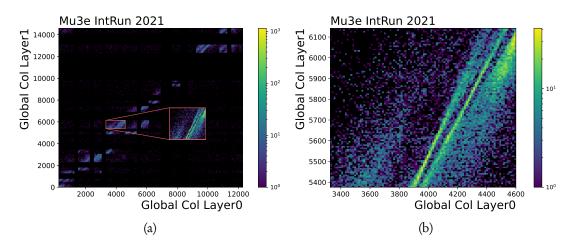

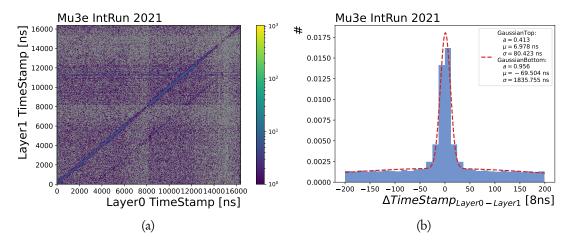

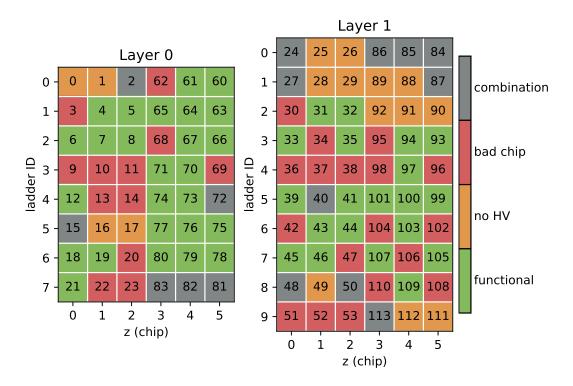

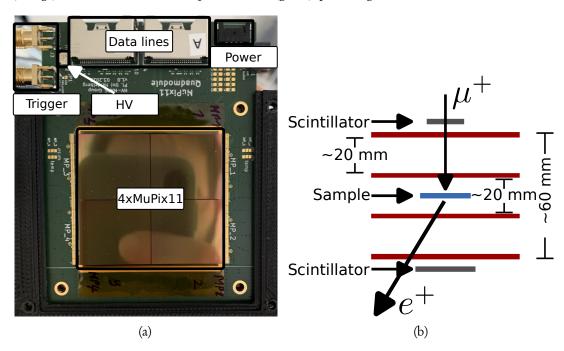

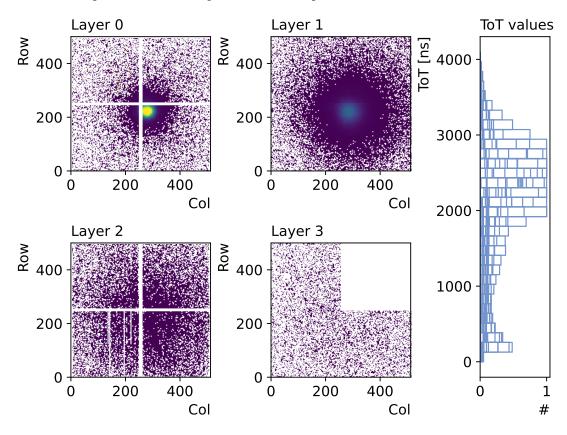

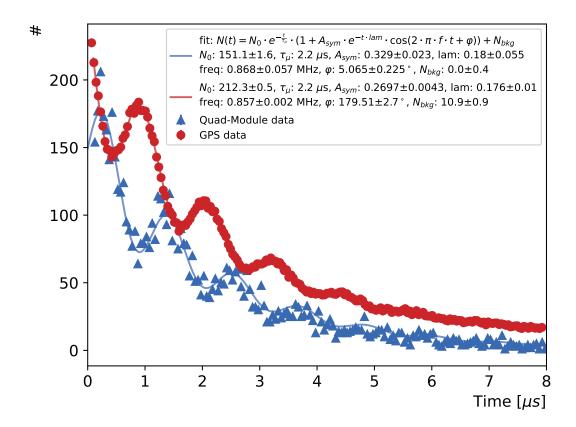

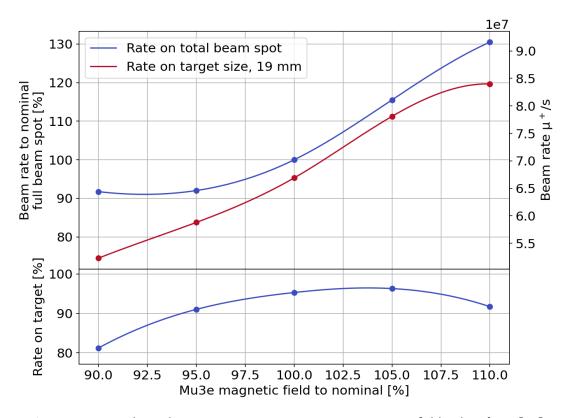

This specific TX operates with an input data width of 8 bits, received as a parallel stream from the FPGA core with a TX core clock (tx coreclkin) running at 125 MHz. Initially, the data flows into the TX first in first out memory (FIFO), which efficiently organises the data buffer, ensuring that the oldest entry is serviced first upon output. Subsequently, the data at the FIFO output is sampled using a different clock (tx clkout) derived from the TX PLL.