EIGER X-ray Detection System for the SLS beamlines

In October 2008 occasioned by the "Tag der offenen Türen" at PSI our running development for a new X-ray Detection System with a frame rate in the 10 kHz range (together with the SLS Detector Group) was presented. One year later we were able to present a fully functional "One Chip Prototype System" read out by a PC from our "Chip Test Board Unit" via a 1 GBit Ethernet-Link. The final version is delivering data from the Detector-Heads via a 10 GBit Ethernet-Link.

Further milestones achieved

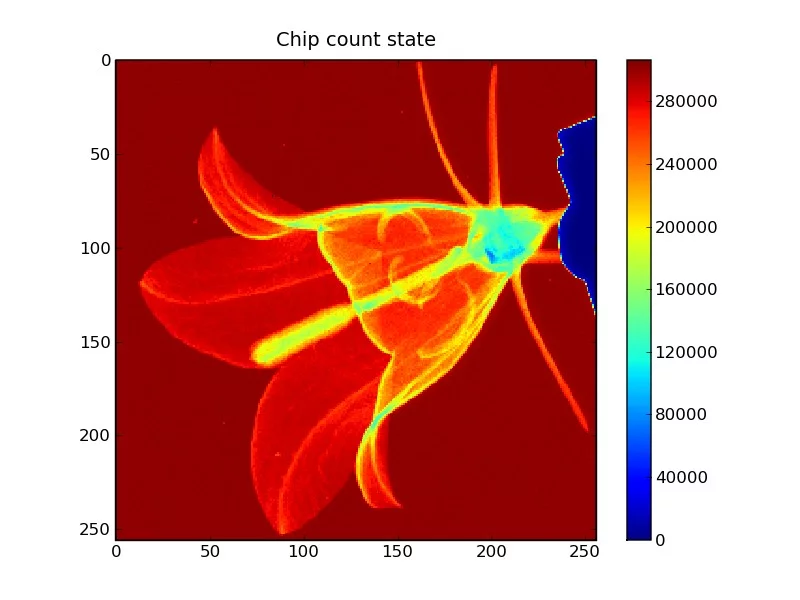

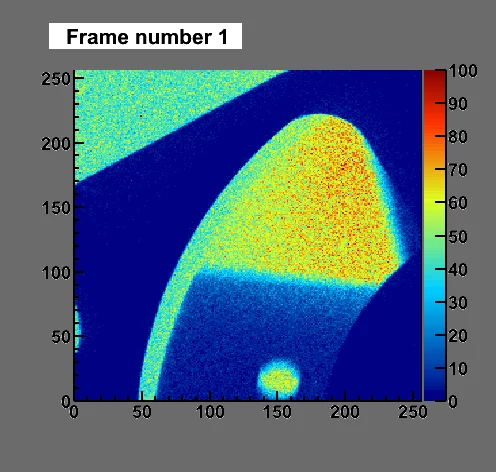

In order to read out EIGER half modules (4 chip units) and EIGER full modules (8 chip units) up to 20'000 times a second, we implemented the required functionalities into two main HW units (Frontend- and Backend-PCB's) according to our Readout Concept for this EIGER Sensor-Modules

LHC/CMS Pixel/Tracker Upgrade

For the future CERN LHC/CMS Pixel/Tracker Detector-System upgrade we already started basic developments in order to improve the Data Readout Rate by a factor of about 4 -- keeping the mass and power budgets constant.

SINQ 2nd Generation Instrumentation

The "2nd Generation SINQ Instrumentation" is developed to replace the first generation data acquisition system in operation at the SINQ diffraction beamlines since 1996.

- This CompactPCI Serial (CPCI-S.0) based new Data AcQuisition system is designed for increased functionality and higher flexibility by fully exploiting the possibilities of state of the art FPGA technologies.

- The beamline specialities are considered by designing beamline specific analog and digital I/O boards for the DAQ-Crate.

- New and/or changed requirements will "easily" be processed by the implementation of additional operating modes into the FPGA Firmware.

- Running prototypes are performing well in daily operation loads @ SINQ beamlines. Furthermore this flexible data acquisition and control system allows for the combination of commercially available standard products and highly specialized FPGA and I/O boards via a customized CompactPCI Serial backplane.

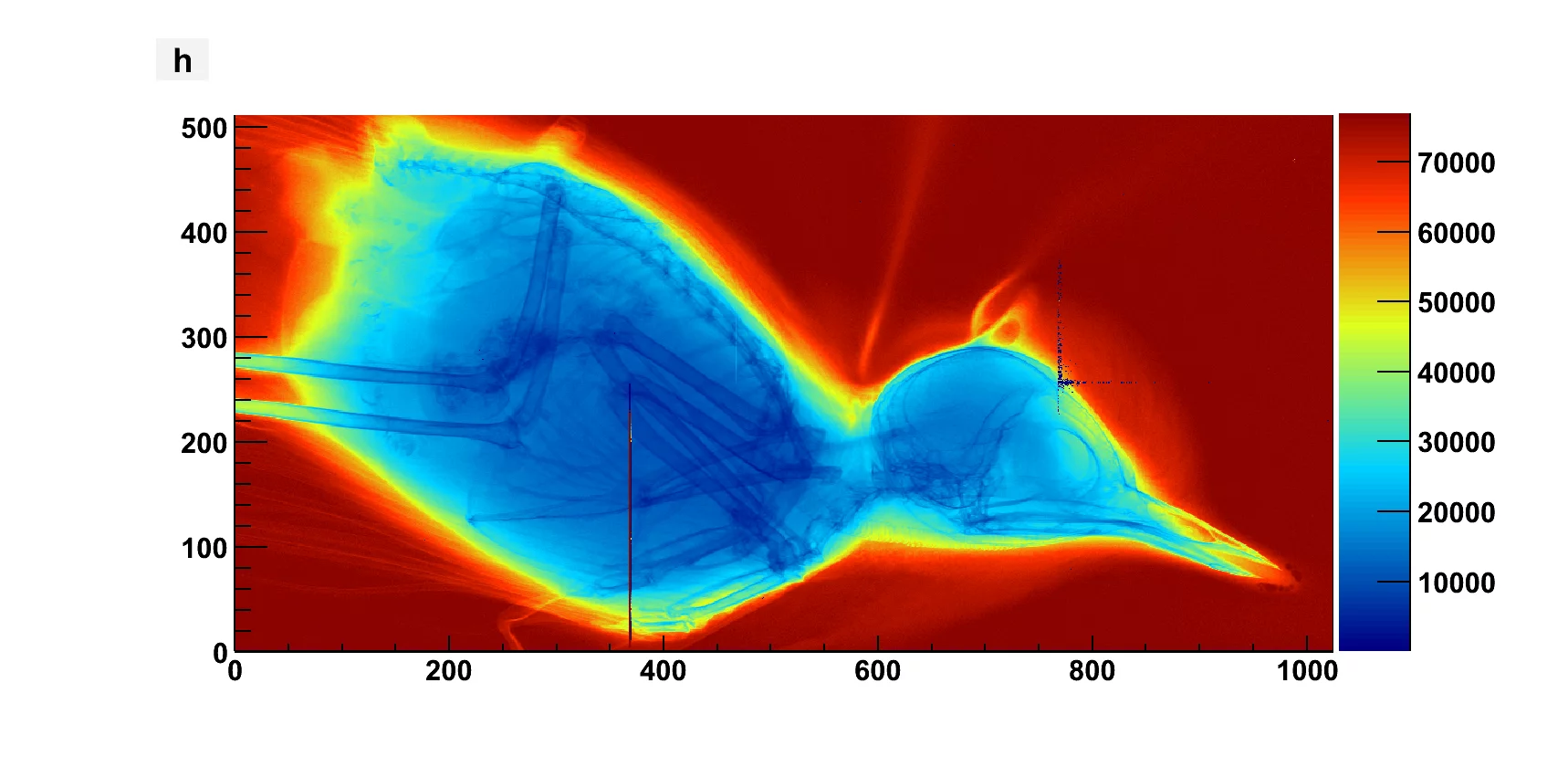

GigaFRoST @ SLS/TOMCAT beamline

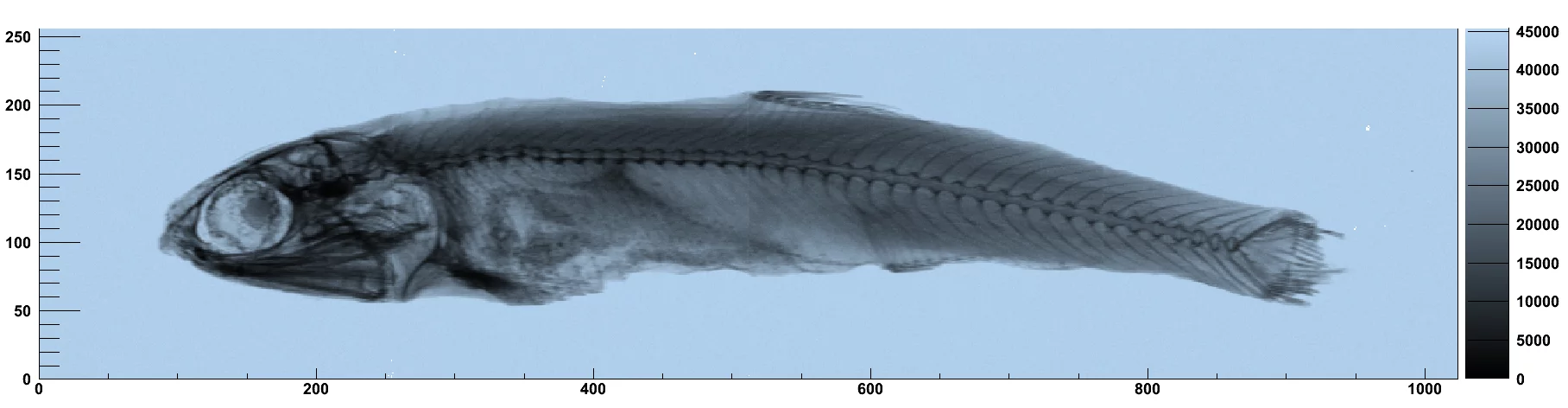

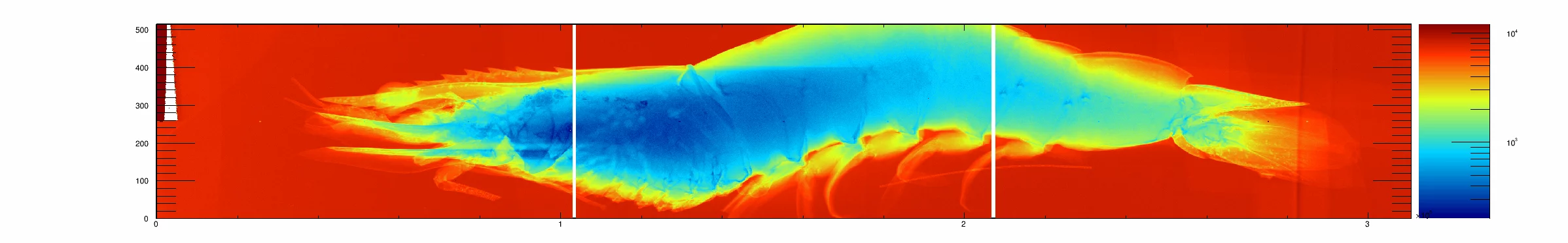

- The technical achievements out of the EIGER readout system development are implemented into the design of an ultra fast and continuous PCO 4 MPixel monochrome CCD camera readout unit ( Giga Fast Readout System for Tomography – rates up to 1'250 frames/sec have been achieved). The continuous data streaming into a specially designed and configured storage system out of commercially available components is realized by 8 optical links with a total capacity of up to 80 GBit/sec. The storage system layout and the processing SW are implemented in close collaboration with our AIT department.

- The very efficient raw data treatement -- i.e. online pixel normalization/calibration within the camera itself -- and the continuous frame readout capability is highly appreciated by scientists. As this kind of camera performance was not available commercially this development was started in order to fulfill the requirements of a continuous use of the available X-ray beam to produce scientific data (i.e. to minimize system dead time).

- Furthermore new types of scientific experiments will become possible do to the continuous data streaming feature of this kind of camera.

"pureCOLD": Chemistry of the heaviest elements known today

Together with the Heavy Elements research group in the Laboratory of Radiochemistry we developed a combined Spectroscopy and Time-Analysis System "pureCOLD" aiming in investigating the chemical properties of the heaviest elements known today with higher sensitivity and accuracy.